- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384797 > OR4E10 (Lineage Power) Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) PDF資料下載

參數(shù)資料

| 型號: | OR4E10 |

| 廠商: | Lineage Power |

| 英文描述: | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| 中文描述: | 現(xiàn)場可編程門陣列(現(xiàn)場可編程門陣列) |

| 文件頁數(shù): | 72/132頁 |

| 文件大小: | 2667K |

| 代理商: | OR4E10 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁當(dāng)前第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁

72

Lucent Technologies Inc.

Preliminary Data Sheet

August 2000

ORCA Series 4 FPGAs

FPGA Configuration Modes

(continued)

5-4488(F

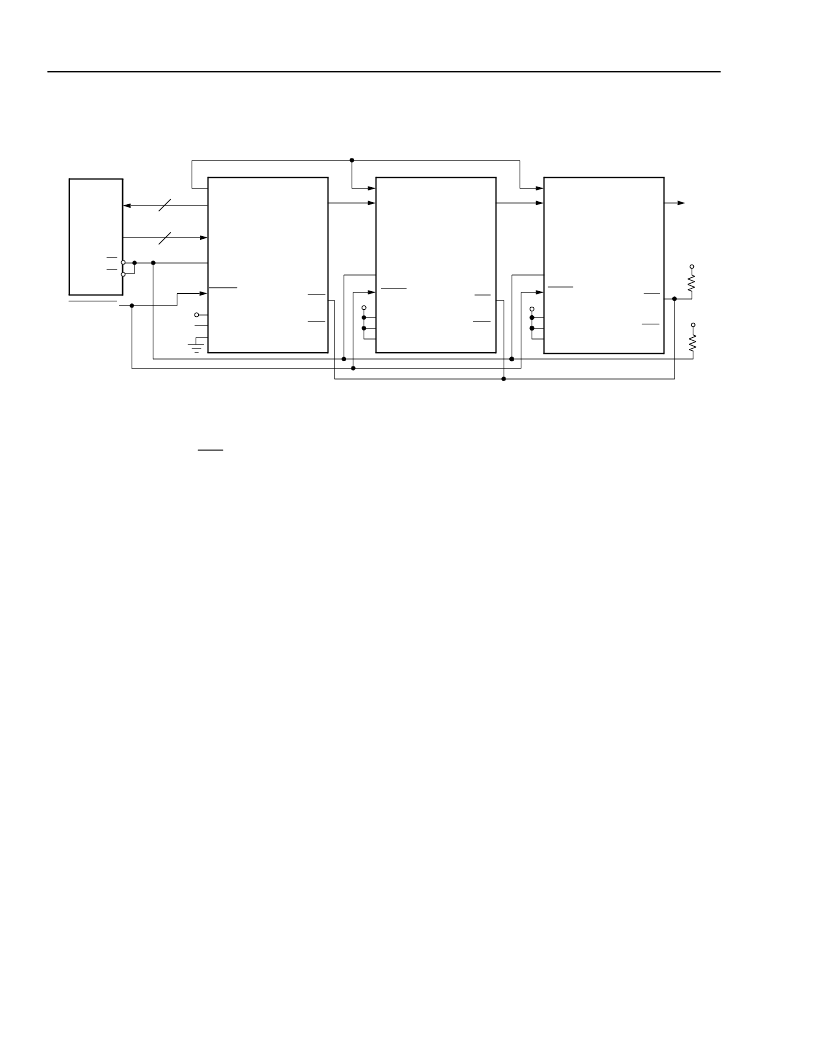

Figure 46. Daisy-Chain Configuration Schematic

V

DD

EPROM

PROGRAM

D[7:0]

OE

CE

A[17:0]

A[17:0]

D[7:0]

DONE

M2

M1

M0

DONE

HDC

LDC

RCLK

CCLK

DIN

DOUT

DOUT

DIN

CCLK

DONE

DOUT

INIT

INIT

INIT

CCLK

V

V

DD

OR

GND

PRGM

PRGM

M2

M1

M0

PRGM

M2

M1

M0

V

DD

V

DD

HDC

LDC

RCLK

HDC

LDC

RCLK

V

DD

ORCA

SERIES

FPGA

SLAVE 2

ORCA

SERIES

FPGA

MASTER

ORCA

SERIES

FPGA

SLAVE 1

As seen in Figure 46, the INIT pins for all of the FPGAs

are connected together. This is required to guarantee

that powerup and initialization will work correctly. In

general, the DONE pins for all of the FPGAs are also

connected together as shown to guarantee that all of

the FPGAs enter the start-up state simultaneously. This

may not be required, depending upon the start-up

sequence desired.

Daisy-Chaining with Boundary Scan

Multiple FPGAs can be configured through the JTAG

ports by using a daisy-chain of the FPGAs. This daisy-

chaining operation is available upon initial configuration

after powerup, after a power-on reset, after pulling the

program pin to reset the chip, or during a reconfigura-

tion if the EN_JTAG RAM has been set.

All daisy-chained FPGAs are connected in series.

Each FPGA reads and shifts the preamble and length

count in on the positive TCK and out on the negative

TCK edges.

An upstream FPGA that has received the preamble

and length count outputs a high on TDO until it has

received the appropriate number of data frames so that

downstream FPGAs do not receive frame start bit

pairs. After loading and retransmitting the preamble

and length count to a daisy chain of downstream

devices, the lead device loads its configuration data

frames.

The loading of configuration data continues after the

lead device had received its configuration read into TDI

of downstream devices on the positive edge of TCK,

and shifted out TDO on the negative edge of TCK.

Absolute Maximum Ratings

Stresses in excess of the absolute maximum ratings

can cause permanent damage to the device. These are

absolute stress ratings only. Functional operation of the

device is not implied at these or any other conditions in

excess of those given in the operations sections of this

data sheet. Exposure to absolute maximum ratings for

extended periods can adversely affect device reliability.

The ORCA Series FPGAs include circuitry designed to

protect the chips from damaging substrate injection

currents and to prevent accumulations of static charge.

Nevertheless, conventional precautions should be

observed during storage, handling, and use to avoid

exposure to excessive electrical stress.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR4E14 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| OR4E2 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| OR4E4 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| OR4E6 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| ORT4622 | Field-Programmable System Chip (FPSC) Four Channel x 622 Mbits/s Backplane Transceiver(現(xiàn)場可編程系統(tǒng)芯片(四通道x 622 M位/秒背板收發(fā)器)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR4E14 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field-Programmable Gate Arrays |

| OR4E2 | 制造商:AGERE 制造商全稱:AGERE 功能描述:Field-Programmable Gate Arrays |

| OR4E2-1BA256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E2-1BA352 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E2-1BA416 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。