- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359670 > MC68HLC705KJ1 (飛思卡爾半導(dǎo)體(中國(guó))有限公司) Computer Operation Properly Module PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HLC705KJ1 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | Computer Operation Properly Module |

| 中文描述: | 電腦操作正確模塊 |

| 文件頁(yè)數(shù): | 54/108頁(yè) |

| 文件大?。?/td> | 718K |

| 代理商: | MC68HLC705KJ1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)

External Interrupt Module (IRQ)

MC68HC705KJ1 MC68HRC705KJ1 MC68HLC705KJ1 Data Sheet, Rev. 4.1

54

Freescale Semiconductor

If edge- and level-sensitive triggering is selected, a rising edge or a high level on a PA0–PA3 pin latches

an external interrupt request. Edge- and level-sensitive triggering allows the use of multiple wired-OR

external interrupt sources. As long as any source is holding a PA0–PA3 pin high, an external interrupt

request is latched, and the CPU continues to execute the interrupt service routine.

If edge-sensitive only triggering is selected, a rising edge on a PA0–PA3 pin latches an external interrupt

request. A subsequent external interrupt request can be latched only after the voltage level of the previous

interrupt signal returns to logic 0 and then rises again to logic 1.

NOTE

The BIH and BIL instructions apply only to the level on the IRQ/V

PP

pin itself

and not to the output of the logic OR function with the PA0

–

PA3 pins. The

state of the individual port A pins can be checked by reading the

appropriate port A pins as inputs.

Enabled PA0

–

PA3 pins cause an IRQ interrupt regardless of whether these

pins are configured as inputs or outputs.

The IRQ pin has an internal Schmitt trigger. The optional external interrupts

(PA0

–

PA3) do not have internal Schmitt triggers.

The interrupt mask bit (I) in the condition code register (CCR) disables all

maskable interrupt requests, including external interrupt requests.

5.4 IRQ Status and Control Register

The IRQ status and control register (ISCR) controls and monitors operation of the IRQ module. All unused

bits in the ISCR read as logic 0s. The IRQF bit is cleared and the IRQE bit is set by reset.

IRQR — Interrupt Request Reset Bit

This write-only bit clears the external interrupt request flag.

1 = Clears external interrupt and IRQF bit

0 = No effect on external interrupt and IRQF bit

IRQF — External Interrupt Request Flag

The external interrupt request flag is a clearable, read-only bit that is set when an external interrupt

request is pending. Reset clears the IRQF bit.

1 = External interrupt request pending

0 = No external interrupt request pending

IRQE — External Interrupt Request Enable Bit

This read/write bit enables external interrupts. Reset sets the IRQE bit.

1 = External interrupt requests enabled

0 = External interrupt requests disabled

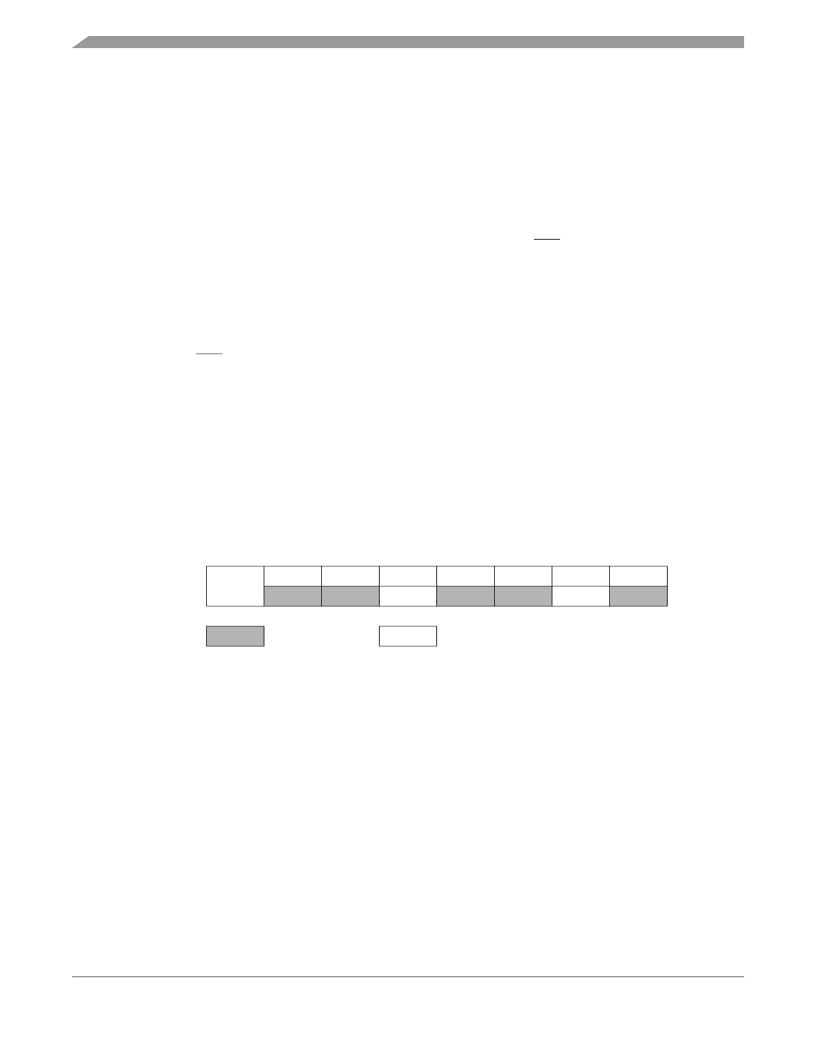

Address:

$000A

Bit 7

6

5

4

3

2

1

Bit 0

Read:

IRQE

0

0

0

IRQF

0

0

0

Write:

R

IRQR

Reset:

1

0

0

0

0

0

0

0

= Unimplemented

R

= Reserved

Figure 5-4. IRQ Status and Control Register (ISCR)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68EC020 | The first full 32-bit implementation of the M68000 family of microprocessors from Motorola |

| MC68EC020FG16 | The first full 32-bit implementation of the M68000 family of microprocessors from Motorola |

| MC68EC020FG25 | The first full 32-bit implementation of the M68000 family of microprocessors from Motorola |

| MC7445ARX933LF | RISC Microprocessor Hardware Specifications |

| MC7445ARX933LG | RISC Microprocessor Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HLC908JK3CP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QT1CFQ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QT4CDW | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QT4CFQ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QY1CDW | 制造商:Rochester Electronics LLC 功能描述:LOW V-1.5K FLASH W/O ADC - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。