- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373065 > K4N26323AE-GC20 (SAMSUNG SEMICONDUCTOR CO. LTD.) 128Mbit GDDR2 SDRAM PDF資料下載

參數(shù)資料

| 型號: | K4N26323AE-GC20 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 128Mbit GDDR2 SDRAM |

| 中文描述: | 128Mbit GDDR2 SDRAM的 |

| 文件頁數(shù): | 25/52頁 |

| 文件大?。?/td> | 826K |

| 代理商: | K4N26323AE-GC20 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

- 25 -

Rev. 1.7 (Jan. 2003)

128M GDDR2 SDRAM

K4N26323AE-GC

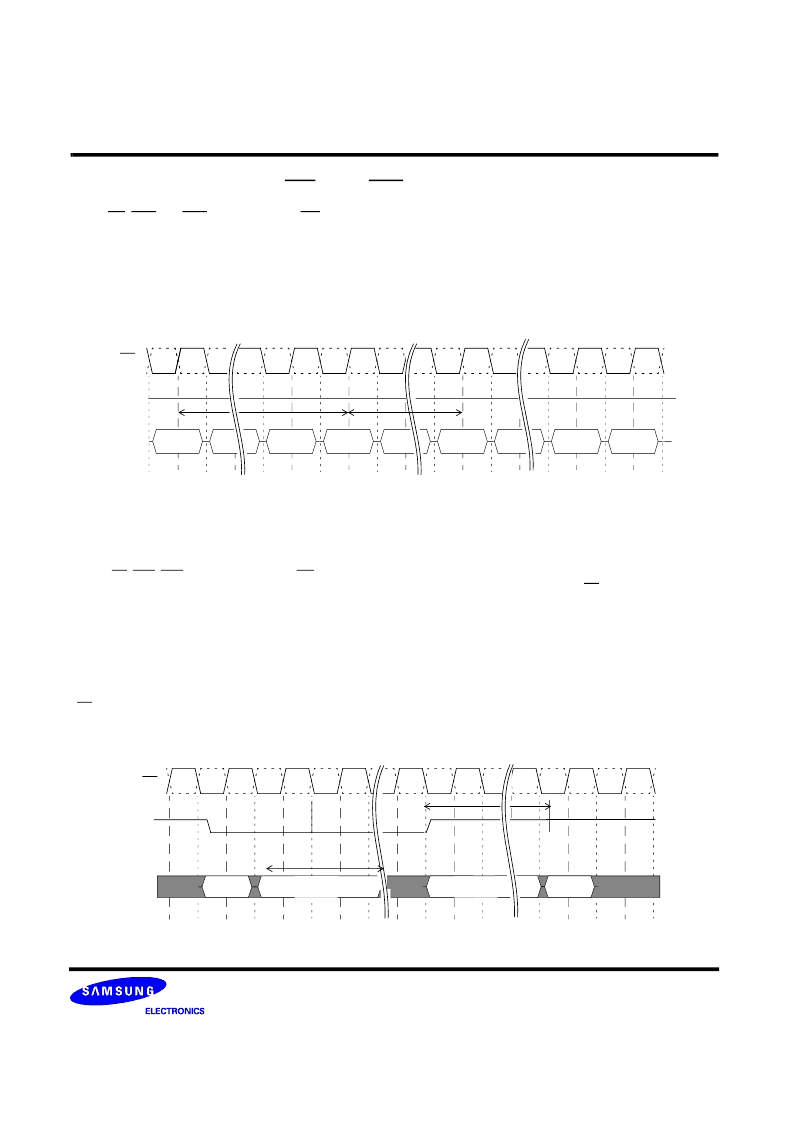

Self Refresh Command

The GDDR2 SDRAM device has a built-in timer to accommodate Self Refresh operation. The Self Refresh Command is defined by

having CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. Once the Self Refresh Command is registered,

CKE must be held low to keep the device in Self Refresh mode and NOP command should be issued or CS should be held high to

ensure stable self refresh operation for next four cycles after the Self Refresh Command. When the GDDR2 SDRAM has entered Self

Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh

Operation to save power. The user may halt the external clock while the device is in Self Refresh mode, however, the clock must be

restarted before the device can exit Self Refresh operation. After CKE is brought high, an internal timer is started to insure CKE is

held high for approximately 10ns before registering the Self Refresh exit command. The purpose of this circuit is to filter out noise

glitches on the CKE input which may cause the GDDR2 SDRAM to erroneously exit Self Refresh operation. Once the Self Refresh

exit command is registered, a delay equal or longer than the tXSA (>20000 tck) must be satisfied before any command can be issued

to the device. CKE must remain high for the entire Self Refresh exit period (tXSA > 20000tCK) and commands must be gated off with

CS held high. Alternatively, NOP commands may be registered on each positive clock edge during the Self Refresh exit interval. (See

Figure.)

CMD

CK, CK

CKE

Self Refresh

CoANY

tXSA (> 20000tCK)

*After self refresh entry, NOP or chip deselect command should be issued during more than 4 cycles

and chip deselet command should be issued for tXSA after self refresh exit.

Automatic Refresh Command (CAS Before RAS Refresh)

When CS, RAS and CAS are held low and WE high at the rising edge of the clock, the chip enters the Automatic Refresh

mode (CBR). All banks of the GDDR2 SDRAM must be precharged and idle for a minimum of the Precharge time (t

RP

)

before the Auto Refresh Command (CBR) can be applied. An address counter, internal to the device, supplies the bank

address during the refresh cycle. No control of the external address bus is required once this cycle has started.

When the refresh cycle has completed, all banks of the GDDR2 SDRAM will be in the precharged (idle) state. A delay

between the Auto Refresh Command (CBR) and the next Activate Command or subsequent Auto Refresh Command

must be greater than or equal to the Auto Refresh cycle time (t

RFC

).

CK, CK

CMD

CBR

Bank

Activate

NOP

NOP

Precharge

CKE

NOP

> = t

RP

> = t

RFC

High

> = 4clk

NOP

NOP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4N26323AE-GC22 | 128Mbit GDDR2 SDRAM |

| K4N26323AE-GC25 | 128Mbit GDDR2 SDRAM |

| K4N56163QF | 256Mbit gDDR2 SDRAM |

| K4N56163QF-GC | 256Mbit gDDR2 SDRAM |

| K4N56163QF-GC25 | 256Mbit gDDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4N26323AE-GC22 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mbit GDDR2 SDRAM |

| K4N26323AE-GC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128Mbit GDDR2 SDRAM |

| K4N27 | 制造商:KODENSHI 制造商全稱:KODENSHI KOREA CORP. 功能描述:Photocoupler(These Photocouplers consist of a Gallium Arsenide Infrared Emitting) |

| K4N28 | 制造商:KODENSHI 制造商全稱:KODENSHI KOREA CORP. 功能描述:Photocoupler(These Photocouplers consist of a Gallium Arsenide Infrared Emitting) |

| K4N29 | 制造商:KODENSHI 制造商全稱:KODENSHI KOREA CORP. 功能描述:Photocoupler(These Photocouplers cosist of a Gallium Arsenide Infrared Emitting) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。