- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385819 > SC4000 (NXP SEMICONDUCTORS) Pressure Transducer, Series 19 mm, Compensated, Pressure Range: 0 psi to 200 psi, Vacuum Gage, 1/8-27 NPT, 10 Vdc excitation PDF資料下載

參數(shù)資料

| 型號: | SC4000 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 路由/交換 |

| 英文描述: | Pressure Transducer, Series 19 mm, Compensated, Pressure Range: 0 psi to 200 psi, Vacuum Gage, 1/8-27 NPT, 10 Vdc excitation |

| 中文描述: | TELECOM, DIGITAL TIME SWITCH, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁數(shù): | 29/52頁 |

| 文件大小: | 179K |

| 代理商: | SC4000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

2000 Sep 07

29

Philips Semiconductors

Preliminary specification

Universal Timeslot Interchange

SC4000

SCbus Alternate (A) Signals Output Enable

(C_23) (Read/Write)

This bit enables the SCbus Alternate

(“A”) Signals Output (when required).

When disabled, the outputs are

tri-stated.

0-> SCbus Alternate (“A”) Signals

Output Disabled (Default)

1-> SCbus Alternate (“A”) Signals

Output Enabled

Configuration Register Byte 3, IAR = 03H

Local bus L_CLK Polarity (C_24)

(Read/Write)

0- > L_CLK Non-Inverted (Default)

1- > L_CLK Inverted

Local bus L_FS Polarity (C_25) (Read/Write)

0- > L_FS Non-Inverted (Default)

1- > L_FS Inverted

Local bus L_FS Position (C_[27:26])

(Read/Write)

00 -> L_FS occurs during the last clock

period of the frame (Default)

01 -> L_FS straddles the frame

boundary

10 -> L_FS occurs during the first clock

period of the frame

11 -> Reserved

Local bus L_CLK & L_FS Rate (C_28)

(Read/Write)

0 -> L_CLK & L_FS equal to the Local

bus data rate (Default)

1 -> L_CLK & L_FS equal to 2 times

the Local bus data rate

Note:

To select the 2x rate, SCLKX2N

must be present or the Local bus fram-

ing mode must be set to a data rate that

is either higher or lower than the SCbus

framing mode.

Local bus L_CLK DPLL Enable (C_29)

(Read/Write)

This mode is provided to maintain a

continuous L_CLK for network inter-

faces during a Clock Fail condition.

0->L_CLK DPLL Disabled (Default)

1->L_CLK DPLL Enabled

Note 1

: The Local bus Framing Mode

(C_[7:6]) must be set to 2.048 Mb/s and

a 65.536MHz Clock must be supplied on

X_IN.

Note 2:

When Enabled L_CLK will run

free during an SCbus Clock Fail

condition.

Note 3: When the DPLL enters the free-

run, the Local bus SO lines are tri-stated.

Local bus L_CLK 8.192 MHz 62.5% Duty

Cycle (C_30) (Read/Write)

0 -> L_CLK 8.192 MHz 62.5% Duty

Cycle Disabled (Default)

1 -> L_CLK 8.192 MHz 62.5% Duty

Cycle Enabled

Note

: To enable L_CLK 8.192 MHz

62.5% Duty Cycle, the Local bus Fram-

ing Mode (C_[7:6]) must be set to 8.192

Mb/s and the SCbus Framing Mode

(C_[5:4]) must be set to 4.096 Mb/s or

2.048 Mb/s. C_28 must be set to 0.

Configuration Register Byte 4, IAR = 04H

Version/Revision Status (C_[39:32])

The Version/Revision Register is a read

only register. It is intended for use to

identify SCxxxx devices.

This field may be changed in future

SCxxxx designs. It is recommended that

a test of this field be included in all ver-

sions of firmware interface code.

The initial release of the SC4000 will be

Version/Revision = 10H

Configuration Register 5,IAR = 05H

Master PLL Reference Select [2:0]

(C_[42:40]) (Read/Write)

When C_43=0 this field selects the refer-

ence for the Internal Master PLL.

000 -> Free-run (Default)

001 -> Free-run

010 -> Free-run

011 -> SREF_8K

100 -> REF_8K_0

101 -> REF_8K_1

110 -> REF_8K_2

111 -> REF_8K_3

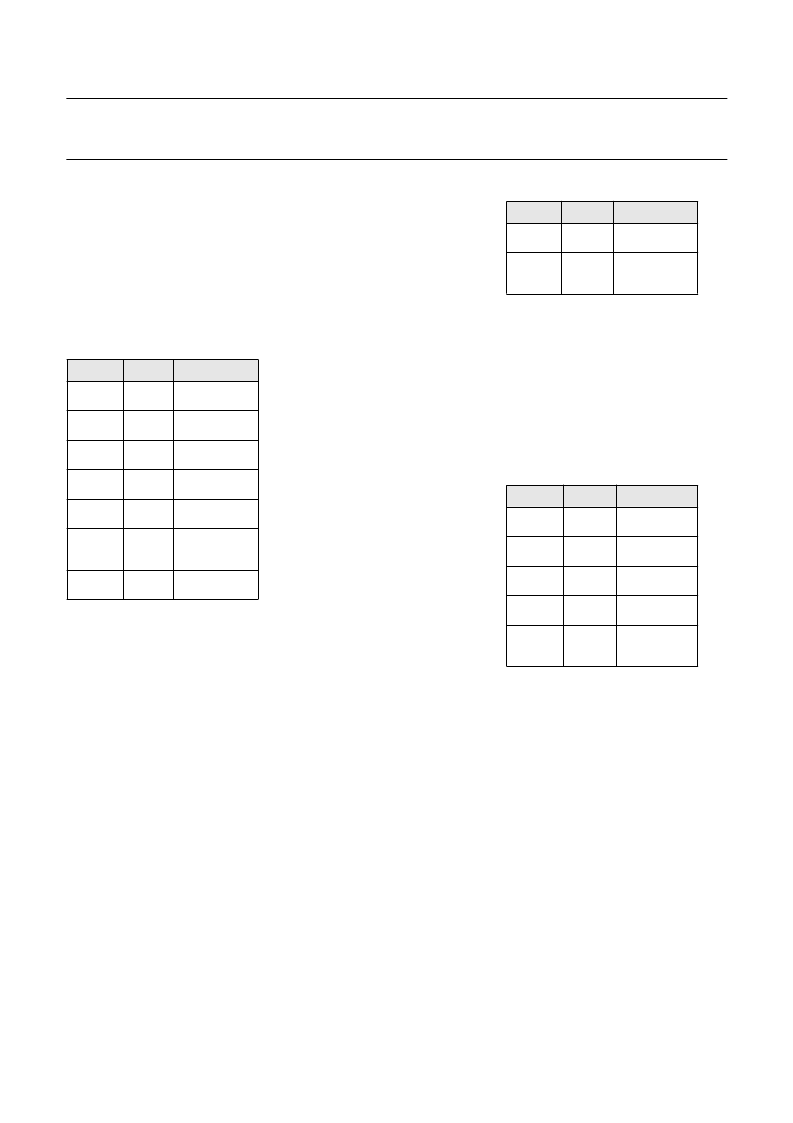

LBDR_[7:0]

C_[31:24]

Definition

0

24

Local bus L_CLK

Polarity

1

25

Local bus L_FS

Polarity

[3:2]

[27:26]

Local bus L_FS

Position [1:0]

4

28

Local bus L_CLK

and L_FS Rate

5

29

Local bus L_CLK

DPLL Enable

6

30

Local bus L_CLK

8.192 MHz 62.5%

duty cycle Enable

7

31

Reserved (0)

(Read only)

LBDR_[7:0]

C_[39:32]

Definition

[3:0]

[35:32]

Revision field (read

only)

[7:4]

[39:36]

Version field (SC4000

= 1H, SC2000 = 0H)

(Read only)

LBDR_[7:0]

C_[47:40]

Definition

[2:0]

[42:40]

Master PLL Reference

Select [2:0]

3

43

Internal/External

Master PLL Select

[5:4]

[45:44]

SCbus SREF_8K

Source Select [1:0]

6

46

SCbus SREF_8K

Output Enable

7

47

SCbus SCLK 8.192

MHz 62.5% duty

cycle enable

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC68C94 | nullQuad universal asynchronous receiver/transmitter QUART |

| SC68C94A1A | nullQuad universal asynchronous receiver/transmitter QUART |

| SC68C94A1N | Pressure Transducer, Series 19 mm, Compensated, Pressure Range: 0 psi to 50 psi, Gage, Cell with body o-ring, 10 Vdc excitation |

| SC68C94C1A | nullQuad universal asynchronous receiver/transmitter QUART |

| SC68C94C1N | Pressure Transducer, Series 19 mm, Compensated, Pressure Range: 0 psi to 50 psi, Gage, flush mount, 10 Vdc excitation |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC4002A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD MODULES SC4002A ( 40 CHARACTERS x 2 LINES ) |

| SC4002ALM-6 | 功能描述:AMPLIFIER TRIP UNIVERSAL INPUT D 制造商:cynergy 3 系列:SC 零件狀態(tài):在售 類型:過程感應(yīng) 跳脫狀態(tài):通電高/低 跳脫范圍:- 延遲時(shí)間:無延遲 電壓 - 電源:16 ~ 30VDC 輸出類型:繼電器 電路:SPDT(1 C 形) 不同電壓時(shí)的觸頭額定電流:3A @ 240VAC 安裝類型:DIN 軌道 工作溫度:0°C ~ 55°C 標(biāo)準(zhǔn)包裝:1 |

| SC4004 | 制造商:Ferraz Shawmut 功能描述: |

| SC4004A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LCD MODULES 40 CHARACTERS x 4 LINES |

| SC4004B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:40 CHARACTERS x 4 LINES |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。