- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372115 > SAA7381 (NXP SEMICONDUCTORS) ATAPI CD-R block decoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7381 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | ATAPI CD-R block decoder |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP144 |

| 文件頁數(shù): | 58/108頁 |

| 文件大小: | 380K |

| 代理商: | SAA7381 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁當(dāng)前第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

1997 Aug 12

58

Philips Semiconductors

Objective specification

ATAPI CD-R block decoder

SAA7381

Table 88

The SAA7381 memory map

Notes

1.

If the SAA7381 is addressed in this area it will not access the DRAM and the data output of the sub-CPU interface

to the microcontroller is disabled. If the SAA7381 host interface has been configured for generic mode and the

address access from FFC0H to FFDFH, a chip select signal is asserted ‘zero’ on the output pin XDA1.

CPU address (bits 23 to 8) = 0. CPU address (bits 7 to 0) = address (bits 7 to 0).

Read in this segment is always from internal the SAA7381 registers. Write is to internal the SAA7381 registers and,

optionally, also to DRAM if debug is set (conf_8051, bit 1 = 1).

CPU address (bits 8 to 0) = address (bits 8 to 0). CPU address (bits 23 to 9) = subseg 1 (bits 12 to 0) + subseg 1

(12 to 0)

×

4 + address (bits 12 to 9).

CPU address (bits 9 to 0) = address (bits 9 to 0). CPU address (bits 23 to 10) = subseg 2

(bits 15 to 2) + address (bits 11 and 10).

CPU address (bits 9 to 0) = address (bits 9 to 0). CPU address (bits 23 to 10) = subseg 1

(bits 15 to 2) + address (bits 15 to 10).

2.

3.

4.

5.

6.

ADDRESS

SEGMENT SIZE

(BYTES)

USED FOR

ADDRESS FUNCTION

FFCOH to FFFFH

FF00H to FFBFH

64

192

the SAA7381s dead space

the SAA7381 register access, debug write

to DRAM

segments in DRAM

subpage 2 in DRAM

subpage 1 in DRAM

subpage 1 in DRAM

none; note 1

none; notes 2 and 3

E000H to FEFFH

D000H to DFFFH

C000H to CFFFH

0000H to BFFFH

7936

4096

4096

49152

note 4

note 5

note 6

notes 1 and 6

In fast RAM mode (see ‘CONF_8051’ bit 7) the lower 48 kbytes of RAM space is not accessible as it is reserved for external ROM.

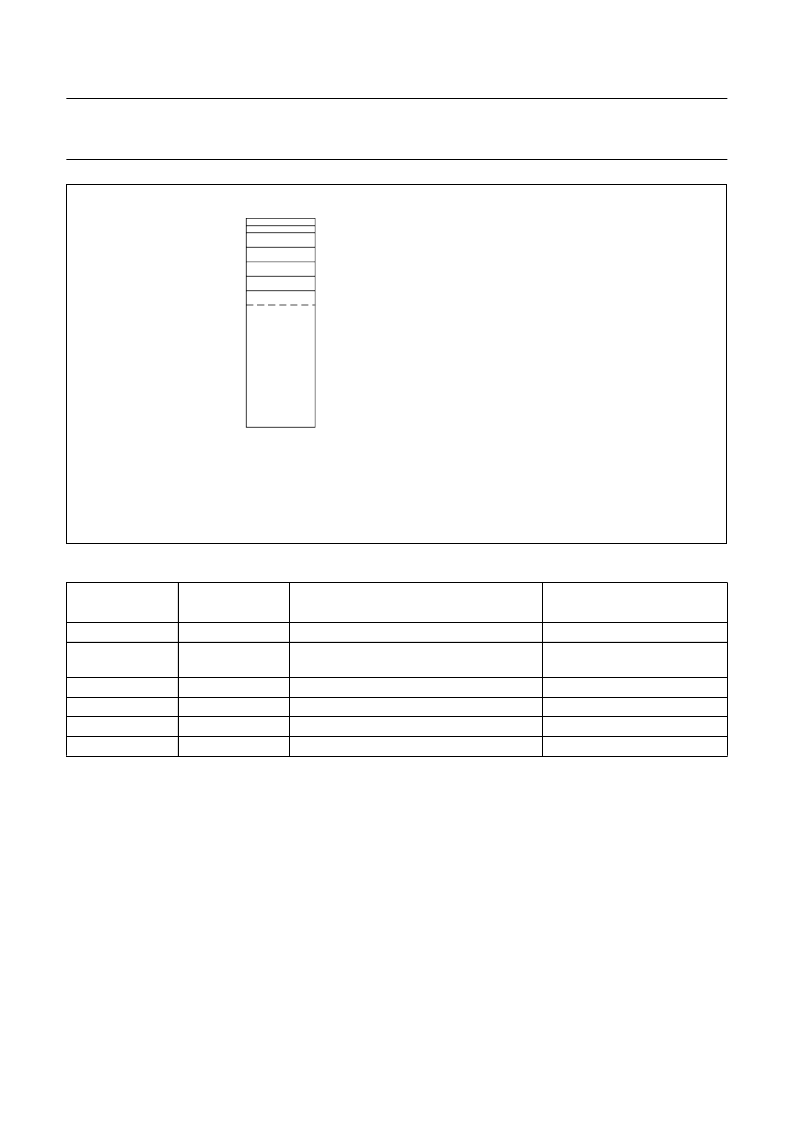

Fig.11 Memory mapping of the SAA7381 registers into 64 kbytes sub-CPU address space.

handbook, full pagewidth

MGK511

subseg 2

subseg 1

subseg 0

subpage 2

7.5 kbits window into 3 CD-ROM blocks

base address is moved in terms of block number

4 kbits always accessible, base address movable in 256 byte pages

top 4 kbits always visible

bottom 48 kbits not usable in fast RAM mode

subpage 1

0XFF00

0XE000

0XD000

0XC000

0X0000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7382GP | Error correction and host interface IC for CD-ROM ELM |

| SAA7382 | Error correction and host interface IC for CD-ROM ELM |

| SAA7390 | High performance Compact Disc-Recordable CD-R controller |

| SAA7390GP | High performance Compact Disc-Recordable CD-R controller |

| SAA7501WP | ARD/ZDF NR.3R1 DIGITAL DECODER|LDCC|68PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7382 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM ELM |

| SAA7382GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM ELM |

| SAA7384 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Terrestrial digital sound decoder for conventional intercarrier PLL-IF systems |

| SAA7385 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM SEQUOIA |

| SAA7385GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM SEQUOIA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。