- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372115 > SAA7381 (NXP SEMICONDUCTORS) ATAPI CD-R block decoder PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7381 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | ATAPI CD-R block decoder |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP144 |

| 文件頁(yè)數(shù): | 43/108頁(yè) |

| 文件大小: | 380K |

| 代理商: | SAA7381 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)當(dāng)前第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)

1997 Aug 12

43

Philips Semiconductors

Objective specification

ATAPI CD-R block decoder

SAA7381

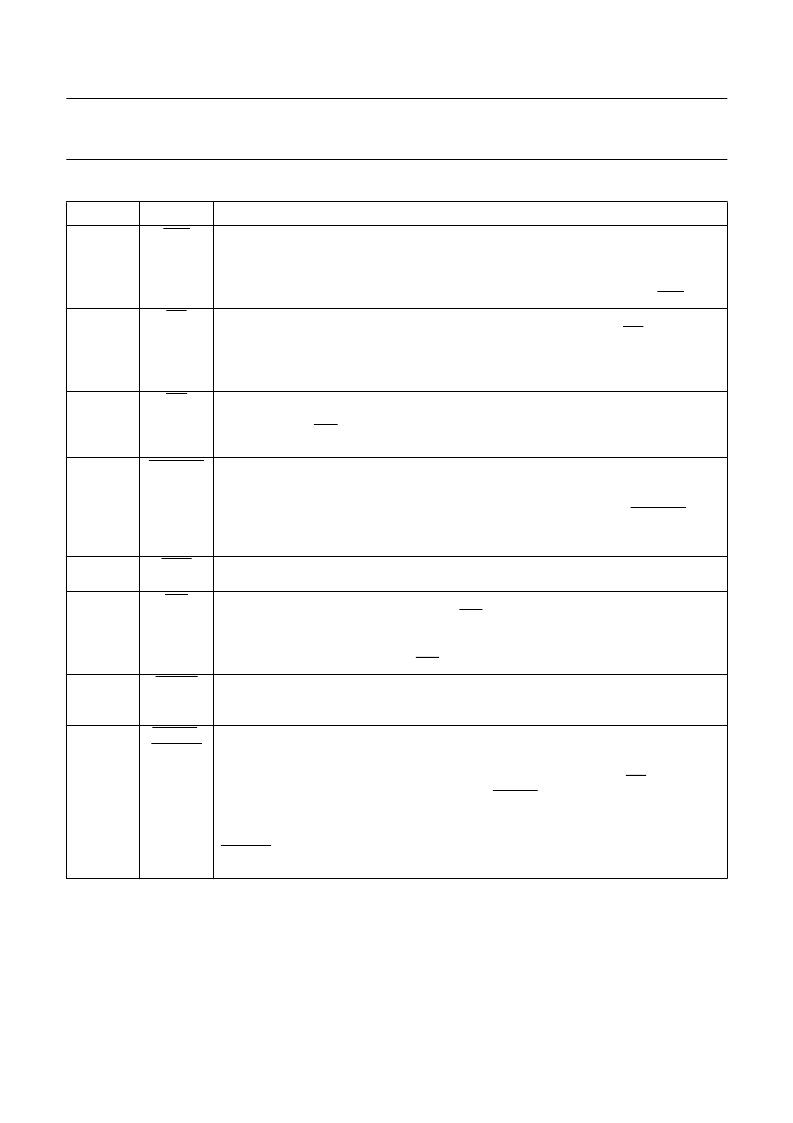

Table 71

Description of the IFSTAT register bits

7.5.3.19

APCMD

During the ATAPI mode this register is used to read the packet command sent by the host. The packet command can

only be received if the appropriate mode has been selected (see DTCTR register; Table 62) and a data transfer has been

started (see DTRG register; see Table 56).

BIT

NAME

DESCRIPTION

7

cmdi

Command interrupt: in the ATAPI mode this bit is asserted when the PC host has written to

the ATAPI command register (see ACMD register; Section 7.5.3.15) and the drive is

selected. It is also asserted when the host writes the execute drive diagnostic command

(90H) to the ATAPI command register, regardless of whether the drive is selected. It is

negated when the microcontroller reads the ACMD register or writes logic 1 to ‘cmdi’.

Data transfer end interrupt: this bit is asserted at the end of data transfer. It is negated

when the microcontroller writes to the DTACK register or writes logic 1 to ‘dtei’. If the ATAPI

mode is selected this bit is also asserted when a packet command has been received and

after a microcontroller memory transfer. The interrupt generated by this bit can be masked

by the auto sequencer.

Auto sequencer data request interrupt: if enabled by ‘drqien’ (IFCTRL; see Table 57), this

bit is asserted after every load of the packet size store into DBCH/DBCL during an ‘a(chǎn)utodrq’

DMA sequence. ‘drqi’ is cleared along with its associated interrupt by the microcontroller

writing logic 1 to ‘drqi’.

Ultra ATA stop before end of transfer interrupt: if enabled by ‘ultra_stopien’ (IFCTRL; see

Table 57), this bit is asserted if the host stops an ultra ATA data transfer before the

TRANSFER COUNTER has reached zero, when ‘a(chǎn)utodrq’ is selected, or before the

DBCH/DBCL task file registers reach zero when ‘a(chǎn)utodrq’ is not selected. ‘ultra_stop’ is

cleared along with its associated interrupt by the microcontroller writing logic 1 to

‘ultra_stop’ (IFSTAT; see Table 70).

Data transfer busy: this bit indicates if a data transfer is taking place. It is asserted by

writing to the DTRG register and is negated at the end of the transfer.

Interrupt/status transfer busy: in ATAPI mode this bit is asserted when the host writes to the

ATAPI device control register and sets the ‘srsti’ bit. It is negated when the microcontroller

reads the ADCTR register or by writing a logic 1 to the ‘srst’ (ADCTR; see Table 68).

It should be noted that if this bit is asserted in the ATAPI mode then the microcontroller

interrupt will also be asserted. The ‘srsti’ interrupt cannot be disabled.

The reset command 08 has been received: this bit indicates that the last command

received was the 08 reset command. Reading the command register ACMD will negate this

bit and its associated interrupt.

The A0 command auto sequence is completed or ultra ATA CRC error flag: this bit

indicates that A0 command auto sequence is completed i.e. the correct A0 command has

been read and the host interface has been configured to receive the 12 byte packet. This

bit does generate an interrupt but should be used in conjunction with the ‘dtei’ interrupt.

A microcontroller write to DTACK will negate the ‘a(chǎn)0comp’ bit.

6

dtei

5

drqi

4

ultra_stop

3

dtbsy

2

srsti

1

reset08

0

a0comp/

crc_error

After an ultra DMA data transfer (read from the SAA7381 or write to the SAA7381) this bit

may be used in conjunction with the DTEI interrupt to indicate data integrity. If the

‘crc_error’ bit = 0 then the last data transfer was corrupt. Again writing to DTACK will

negate this bit.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7382GP | Error correction and host interface IC for CD-ROM ELM |

| SAA7382 | Error correction and host interface IC for CD-ROM ELM |

| SAA7390 | High performance Compact Disc-Recordable CD-R controller |

| SAA7390GP | High performance Compact Disc-Recordable CD-R controller |

| SAA7501WP | ARD/ZDF NR.3R1 DIGITAL DECODER|LDCC|68PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7382 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM ELM |

| SAA7382GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM ELM |

| SAA7384 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Terrestrial digital sound decoder for conventional intercarrier PLL-IF systems |

| SAA7385 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM SEQUOIA |

| SAA7385GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Error correction and host interface IC for CD-ROM SEQUOIA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。