- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382385 > PCT1789N PCT303DL PDF資料下載

參數(shù)資料

| 型號(hào): | PCT1789N |

| 英文描述: | PCT303DL |

| 中文描述: | PCT303DL |

| 文件頁數(shù): | 19/40頁 |

| 文件大?。?/td> | 632K |

| 代理商: | PCT1789N |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

PC-TEL, Inc.

28

1789N0DOCDAT01A-0399

PCT1789N DATA SHEET

303DL F

UNCTIONAL

D

ESCRIPTION

!

PRELIMINARY

PRELIMINARY

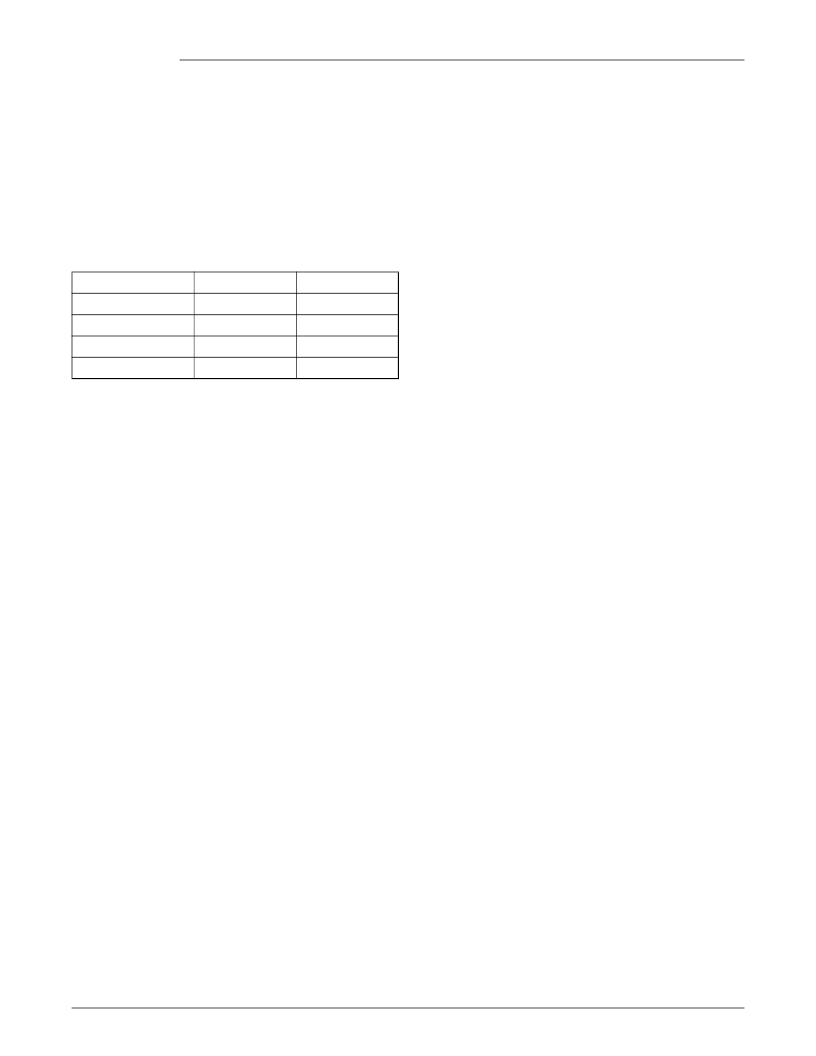

Revision Identification

The 303DL provides the system designer the ability to

determine the revision of the PCT303D and/or the

PCT303L. Register 11 identifies the revision of the

PCT303D with 4 bits named REVA. Register 13

identifies the revision of the PCT303L with 4 bits named

REVB. Table 11 shows the values for the various

revisions.

In-Circuit Testing

The 303DL’s advanced design provides the modem

manufacturer with increased ability to determine system

functionality during production line tests, as well as

support for end-user diagnostics. Four loopback modes

allow increased coverage of system components. For

three of the test modes, a line-side power source is

needed. While a standard phone line can be used, the

test circuit in Figure 22 on page 59 is adequate. In

addition, an off-hook sequence must be performed to

connect the power source to the line-side chip.

For the start-up test mode, no line-side power is

necessary and no off-hook sequence is required. The

start-up test mode is enabled by default. When the PDL

bit (register 6, bit 4) is set (the default case), the line side

is in a power-down mode and the DSP side is in a digital

loop-back mode. In this mode, data received on SDI is

passed through the internal filters and transmitted on

SDO. This path introduces approximately 0.9 dB of

attenuation on the SDI signal received. The group delay

of both transmit and receive filters exists between SDI

and SDO. Clearing the PDL bit disables this mode and

the SDO data is switched to the receive data from the

line side. Note, when PDL is cleared the FDT bit

(register 12, bit 6) becomes active, indicating the

successful communication between the line side and

DSP side. This can be used to verify that the ISOcap is

operational.

The remaining test modes require an off-hook sequence

to operate. The following sequence defines the off-hook

requirement:

1. Power up or reset.

2. Program clock generator to desired sample rate.

3. Enable line side by clearing PDL bit.

4. Issue off-hook

5. Delay 4608/Fs to allow calibration to occur.

6. Set desired test mode.

The ISOcap digital loopback mode allows the data pump

to provide a digital input test pattern on SDI and receive

that digital test pattern back on SDO. To enable this

mode, set the DL bit of register 1. In this mode, the

isolation barrier is actually being tested. The digital

stream is delivered across the isolation capacitor, C1 of

Figure 2 on page 6, to the line side device and returned

across the same barrier. Note in this mode, the 0.9 dB

attenuation and filter group delays also exist.

The analog loopback mode allows an external device to

drive the RX pin of the line side chip and receive the

signal from the TX pin. This mode allows testing of

external components connecting the RJ-11 jack (tip and

ring) to the line side of the 303DL. To enable this mode,

set the AL bit of register 2.

The final testing mode, internal analog loopback, allows

the system to test the basic operation of the transmit/

receive path of the line side and the external

components R4, R8, and C5 of Figure 2 on page 6. In

this test mode, the data pump provides a digital test

waveform on SDI. This data is passed across the

isolation barrier, looped from the TX to RX pin, passed

back across the isolation barrier, and presented to the

data pump on SDO. To enable this mode, clear the HBE

bit of register 2.

When the HBE bit is cleared, this causes a DC offset

which affects the signal swing of the transmit signal. In

this test mode, it is recommended that the transmit

signal be 12 dB lower than normal transmit levels. This

lower level eliminates clipping caused by the DC offset

which results from disabling the hybrid. It is assumed in

this test that the line AC impedance is nominally 600

.

NOTE: All test modes are mutually exclusive. If more

than one test mode is enabled concurrently, the results

are unpredictable.

Exception Handling

The 303DL provides several mechanisms to determine

if an error occurs during operation. Through the

secondary frames of the serial link, the controlling DSP

can read several status bits. The bit of highest

importance is the frame detect bit (FDT, register 12 bit

6). This bit indicates that the DSP side (PCT303D) and

line side (PCT303L) devices are communicating. During

Table 11 Revision Values

Revision

A

B

C

D

PCT303D

1000

1001

–

–

PCT303W

–

–

–

0100

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCV250TWG5 | |

| PCV250TWLY5 | |

| PCV250TWO5 | |

| PCV250TWPG5 | |

| PCV250TWR5 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCT-178F-Q | 制造商:Panduit Corp 功能描述: |

| PCT-179F-Q | 制造商:Panduit Corp 功能描述:Call vendor for pricing |

| PCT-18 | 制造商:Stancor 功能描述: |

| PCT-182F-Q | 制造商:Panduit Corp 功能描述: |

| PCT-1861 | 制造商:MICRO-ELECTRONICS 制造商全稱:Micro Electronics 功能描述:MODEM TRANSFORMER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。