- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1012 Phase Lock Loop (PLL) IC; Number of Circuits:1; Package/Case:14-DIP; Mounting Type:Through Hole PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-1012 |

| 英文描述: | Phase Lock Loop (PLL) IC; Number of Circuits:1; Package/Case:14-DIP; Mounting Type:Through Hole |

| 中文描述: | 4Low成本千兆速率發(fā)送/接收芯片組 |

| 文件頁數(shù): | 40/42頁 |

| 文件大小: | 321K |

| 代理商: | HDMP-1012 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁

612

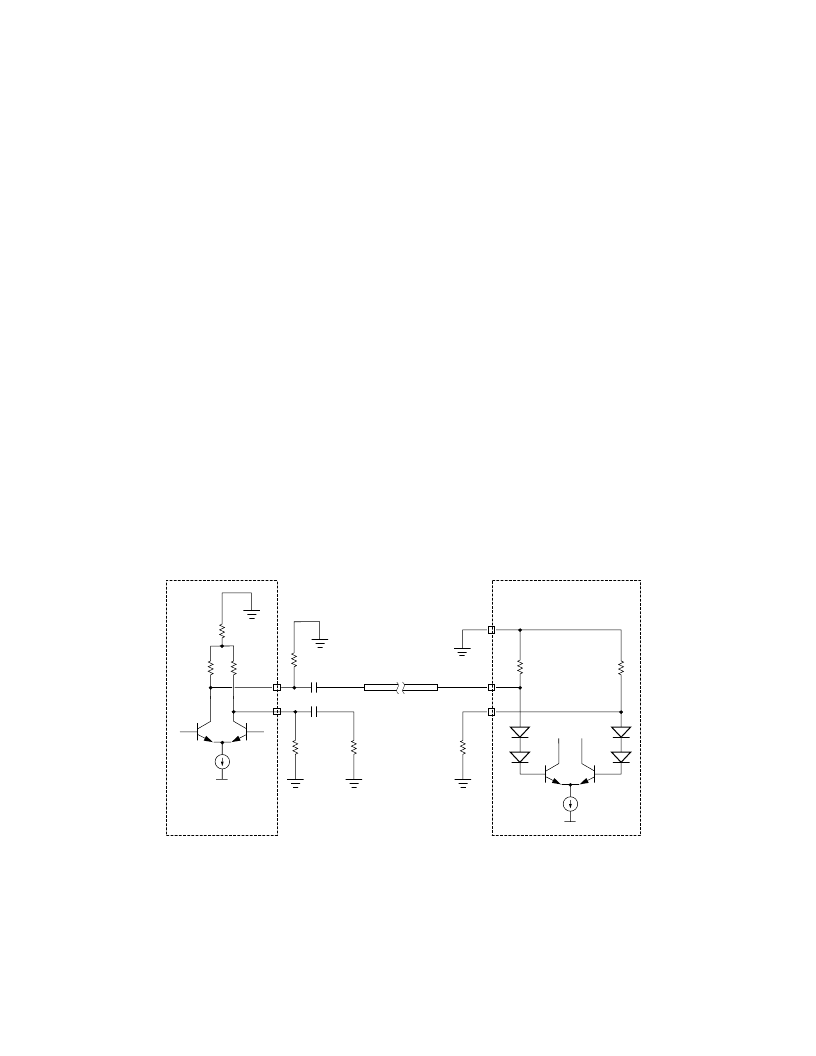

deliver ECL swings directly into

50

. The output impedance is

matched to 50

with a VSWR of

less than 2:1 to above 2 GHz. This

output is ideal for driving the I-

H50 input through a 50

cable

and a 0.1 uF coupling capacitor.

The 150

shunt resistor to

ground improves internal DC bias

of the O-BLL differential output

circuit. The O-BLL driver can also

be connected directly into a high

speed 50

oscilloscope. For

optimum performance, both

output should see the same

impedance. It is necessary that all

used O-BLL outputs be

terminated into 50

. Figure 23

shows various methods of

interfacing O-BLL to I-H50 and

standard ECL logic.

TTL and Positive 5 V

Operation

Many applications require the I/

Os to interface to the standard

TTL logic family. Such TTL/ECL

translators are available in the

industry from various

semiconductor manufacturers.

This works well, but requires two

power supplies since the system is

supporting two different logic

families. This technique is

preferred, since it is easier to

keep a single clean ground plane.

Although G-LINK has been

designed to work with conven-

tional ECL negative supply, a

single positive supply can also be

used. This basically replaces the

traditional ground and Vee planes

with the Vcc and ground planes.

Also, the termination plane Vtt is

shifted up to +3 V. In theory,

since voltages are all relative,

there should be no difference. In

practice, however, the differences

lie in how well the Vcc plane is

bypassed to ground, since all of

the I/Os are referenced to this

plane. It is therefore necessary to

separate any TTL or CMOS Vcc to

this chip set, so that the cleanest

Vcc plane can be achieved.

Figure 22. I-H50 and O-BLL Simplified Circuit Schematic.

Z

O

= 50

V

EE

V

EE

28 mA

80

80

50

150

150

50

50

12

O-BLL

I-H50

HGND

0.1 μF

50

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1014 | Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 |

| HDMP-1022 | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1014 | 制造商:Hewlett Packard Co 功能描述: |

| HDMP-1022 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。