- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1012 Phase Lock Loop (PLL) IC; Number of Circuits:1; Package/Case:14-DIP; Mounting Type:Through Hole PDF資料下載

參數(shù)資料

| 型號: | HDMP-1012 |

| 英文描述: | Phase Lock Loop (PLL) IC; Number of Circuits:1; Package/Case:14-DIP; Mounting Type:Through Hole |

| 中文描述: | 4Low成本千兆速率發(fā)送/接收芯片組 |

| 文件頁數(shù): | 17/42頁 |

| 文件大小: | 321K |

| 代理商: | HDMP-1012 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

589

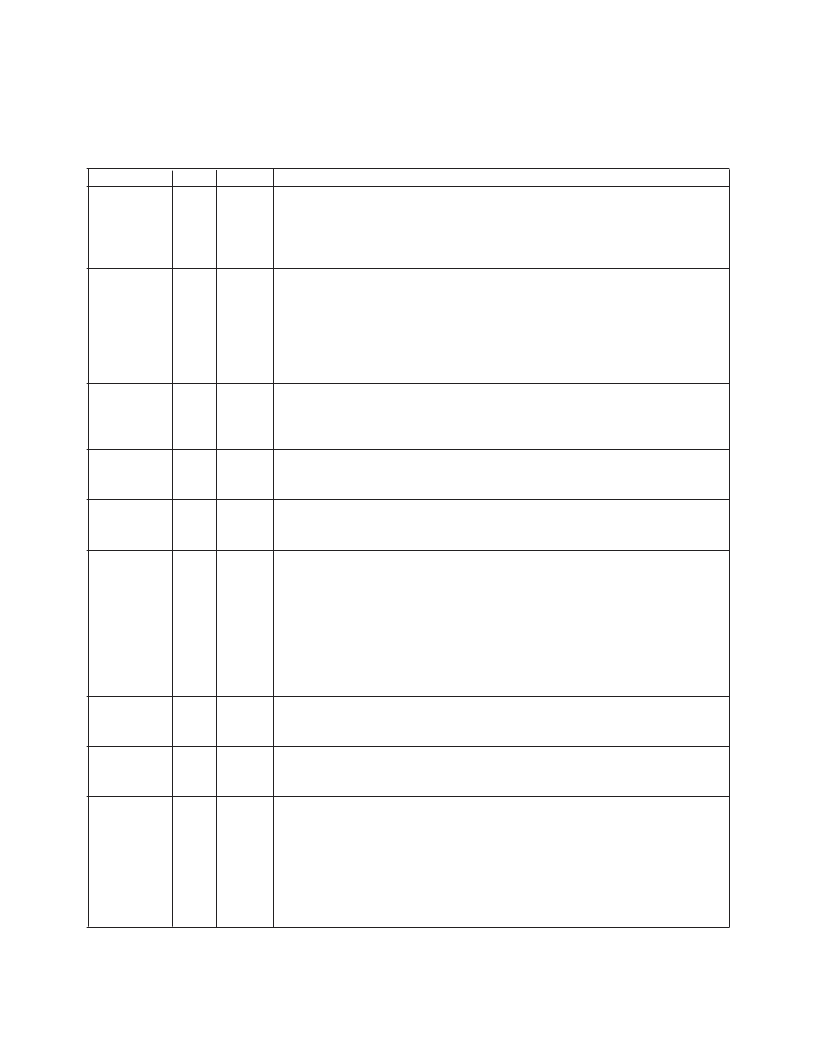

Tx I/O Definition (cont’d.)

Name

INV

Pin

25

Type

O-ECL

Signal

Invert Signal:

A high value of INV implies that the current frame is

being sent inverted to maintain long-term DC balance. With a buffer,

or pulled down with a 1K resistor to V

EE

and ac coupled, this signal

is useful as an aid to analyzing the serial output stream with an

oscilloscope.

Loop In-lock Indication:

This signal indicates the lock status of the

Tx PLL. A high value indicates lock. This signal is normally connected

to the SMTRST1 reset input of the Rx state machine to force the link

into the start-up state until the Tx PLL has locked. This signal may

give multiple false-lock indications during the acquisition process, so

should be debounced if it is used for any other purpose than to drive

the Rx chip.

Loop Back Control:

Input which controls whether the DOUT,

DOUT*, or the LOUT, LOUT* outputs are currently enabled. If active,

LOUT, LOUT* are enabled. The unused output is powered down to

reduce dissipation.

Loop Back Serial Data Output:

Output used when LOOPEN is

active. Typically this output will be used to drive the LIN, LIN* inputs

of the Rx chip.

16 or 20 Bit Word Select:

When this signal is high, the link operates

in 20 Bit data transmission mode. Otherwise, the link operates in

16 Bit mode.

Select Double Frame Mode:

When this signal is high, the PLL

expects a 1/2 speed parallel clock at STRBIN. The chip then internally

multiplies this clock and produces a full-rate parallel clock at

STRBOUT. Note that the phase relationship of STRBIN to STRBOUT

and the sampling point change with asserting MDFSEL, as shown in

the Tx timing diagram. This feature is provided so that either a 40 bit

or 32 bit word can be easily transmitted as two 20, or two 16 bit

words. When MDFSEL is low, the PLL expects a full-rate parallel

clock at STRBIN.

Ready for Data:

Output to tell the user the Link is ready to

transmit data. This pin is a retimed version of the ED input, which is

driven by the Rx chip state machine controller.

Chip Reset:

This active-low pin initializes the internal chip registers.

It should be asserted during power up for a minimum of 5 parallel-

rate clock cycles to ensure a complete reset.

Data Clock Input:

When EHCLKSEL is low, this input is phase

locked and multiplied to generate the high speed serial clock. The chip

expects a clock frequency which is equal to the input frame rate if

MDFSEL (double frame mode) is low, and 1/2 the frame rate if

MDFSEL is high. When EHCLKSEL is high, the PLL is bypassed,

and STRBIN directly becomes the high speed serial clock. Refer to

the Tx Timing diagram for the phase relationship between STRBIN,

data and STRBOUT.

LOCKED

75

O-ECL

LOOPEN

16

I-ECL

LOUT

LOUT*

14

15

O-BLL

M20SEL

73

I-ECL

MDFSEL

74

I-ECL

RFD

65

O-ECL

RST*

34

I-ECL

STRBIN

STRBIN*

8

9

I-H50

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1014 | Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 |

| HDMP-1022 | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1014 | 制造商:Hewlett Packard Co 功能描述: |

| HDMP-1022 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。