- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97930 > EPF8482A Programmable Logic PDF資料下載

參數(shù)資料

| 型號: | EPF8482A |

| 英文描述: | Programmable Logic |

| 中文描述: | 可編程邏輯 |

| 文件頁數(shù): | 48/61頁 |

| 文件大小: | 979K |

| 代理商: | EPF8482A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當(dāng)前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

52

Altera Corporation

FLEX 8000 Programmable Logic Device Family Data Sheet

Operating Modes

The FLEX 8000 architecture uses SRAM elements that require

configuration data to be loaded whenever the device powers up and

begins operation. The process of physically loading the SRAM

programming data into the device is called configuration. During

initialization, which occurs immediately after configuration, the device

resets registers, enables I/O pins, and begins to operate as a logic device.

The I/O pins are tri-stated during power-up, and before and during

configuration. The configuration and initialization processes together are

called command mode; normal device operation is called user mode.

SRAM elements allow FLEX 8000 devices to be reconfigured in-circuit

with new programming data that is loaded into the device. Real-time

reconfiguration is performed by forcing the device into command mode

with a device pin, loading different programming data, reinitializing the

device, and resuming user-mode operation. The entire reconfiguration

process requires less than 100 ms and can be used to dynamically

reconfigure an entire system. In-field upgrades can be performed by

distributing new configuration files.

Conguration Schemes

The configuration data for a FLEX 8000 device can be loaded with one of

six configuration schemes, chosen on the basis of the target application.

Both active and passive schemes are available. In the active configuration

schemes, the FLEX 8000 device functions as the controller, directing the

loading operation, controlling external EPROM devices, and completing

the loading process. The clock source for all active configuration schemes

is an oscillator on the FLEX 8000 device that operates between 2 MHz and

6 MHz. In the passive configuration schemes, an external controller

guides the FLEX 8000 device. Table 14 shows the data source for each of

the six configuration schemes.

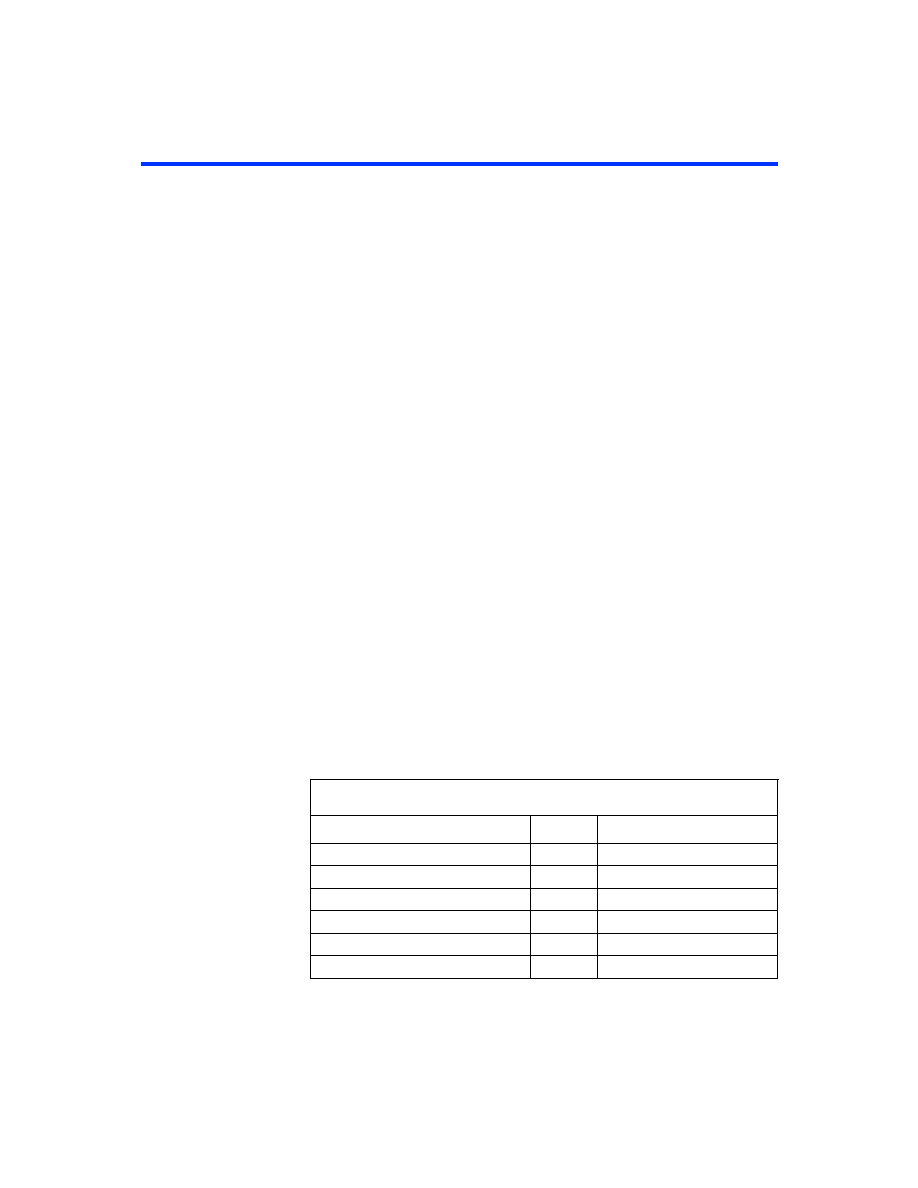

Table 14. Data Source for Configuration

Configuration Scheme

Acronym

Data Source

Active serial

AS

Altera Configuration EPROM

Active parallel up

APU

Parallel EPROM

Active parallel down

APD

Parallel EPROM

Passive serial

PS

Serial data path

Passive parallel synchronous

PPS

Intelligent host

Passive parallel asynchronous

PPA

Intelligent host

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EPIC | EPiC Family Product Line (304k) |

| EPL10P8BD | UV-Erasable/OTP PLD |

| EPL10P8BP | UV-Erasable/OTP PLD |

| EPL12P6BD | UV-Erasable/OTP PLD |

| EPL241ED | UV-Erasable/OTP PLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF8636A | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Programmable Logic Device Family |

| EPF8636AGC192-2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| EPF8636AGC192-3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| EPF8636AGC192-4 | 制造商:Altera Corporation 功能描述:Field-Programmable Gate Array, 504 Cell, 192 Pin, Ceramic, PGA |

| EPF8636AGC192-5 | 制造商:Altera Corporation 功能描述:Field-Programmable Gate Array, 504 Cell, 192 Pin, Ceramic, PGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。