- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376802 > DM9102 (Electronic Theatre Controls, Inc.) Single Chip Fast Ethernet NIC controller PDF資料下載

參數(shù)資料

| 型號: | DM9102 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Single Chip Fast Ethernet NIC controller |

| 中文描述: | 單芯片快速以太網(wǎng)網(wǎng)卡控制器 |

| 文件頁數(shù): | 9/77頁 |

| 文件大小: | 459K |

| 代理商: | DM9102 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

DM9102A

Single Chip Fast Ethernet NIC controller

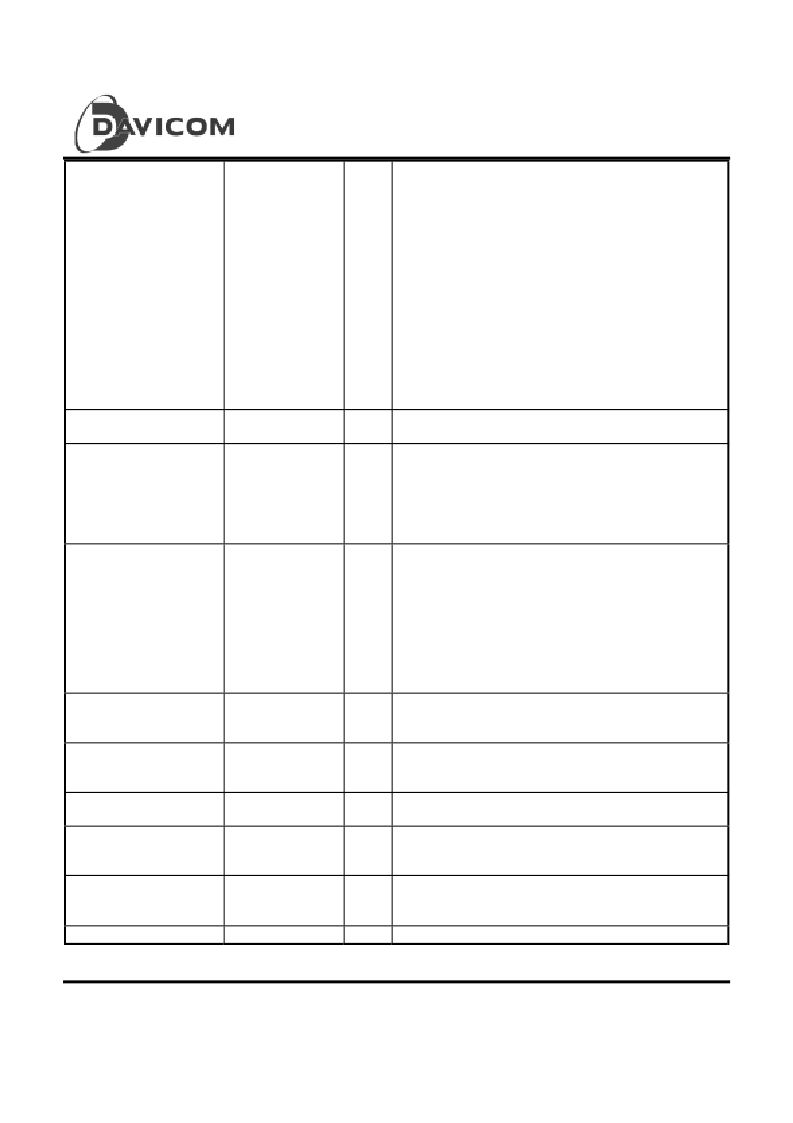

the WOL as pulse or DC signal.

0 = WOL pulse mode (default)

1 = WOL DC mode

BPAD2 is also a reset latch pin. It is Boot ROM address and

data bus when normal operation. When at power on reset, it is

used to pull up or down externally through a resister to select

the PME as pulse or DC signal.

0 = PME pulse mode (default)

1 = PME DC mode

BPAD7 is also a reset latch pin. It is Boot ROM address and

data bus when normal operation. When at power on reset, it is

used to pull up or down externally through a resister to select

LED mode.

0 = LED mode 0 (default)

1 = LED mode 1

72

BPCS#

O

Boot ROM Chip Select

Boot ROM or external register chip select signal.

73

BPA0/WMODE

O, LI

Boot ROM address line/WOL mode selection

This multiplexed pin acts as boot ROM address bit 0 output

signal during normal operation. When at power on reset, it

used to select the type of WOL signal.

0 = WOL high active (default)

1 = WOL low active

74

BPA1/PCIMODE#

I/O, LI Boot ROM address line / PCI mode selection

This multiplexed pin acts as the boot ROM address bit 1 output

signal during normal operation. When RST# is active (low), it

acts as the input system type. If the DM9102A is used in a

CardBus system, this pin should be connected to a pull-up

resistor; otherwise, the DM9102A consider the host as a PCI

system.

0 = PCI mode (default)

1 = CardBus mode

77

EEDI

I

EEPROM Data In

The DM9102A will read the contents of EEPROM serially

through this pin.

78

EEDO

O

EEPROM Data Out

The DM9102A will use this pin to serially write opcodes,

addresses and data into the EEPROM.

79

EECK

O

EEPROM Serial Clock

This pin provides the clock for the EEPROM data transfer.

80

EECS

O

EEPROM Chip Select

This pin will enable the EEPROM during loading of the

Configuration Data.

81

SELROM

I

Multiplex or Director mode selection

0 = Multiplex mode (default)

1 = Direct mode

83,84,85,91,92,93,94

NC

NC

In Multiplex mode, these pins are not connected.

Final

Version: DM9102A-DS-F03

August 28, 2000

9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9102A | Single Chip Fast Ethernet NIC controller |

| DM9102AF | Single Chip Fast Ethernet NIC controller |

| DM9102AT | Single Chip Fast Ethernet NIC controller |

| DM9108APPLICATIONENGINEERINGNOTESONE | DM9108 Application Engineering notes one |

| DM9108APPLICATIONENGINEERINGNOTESTHREE | DM9108 Application Engineering notes three |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9102A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102AF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102AT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single Chip Fast Ethernet NIC controller |

| DM9102D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE CHIP FAST ETHEMET NIC CONTROLLER |

| DM9102DE | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Single Chip Fast Ethernet NIC Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。