- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382924 > DAC1627D1G25 (NXP SEMICONDUCTORS) PDF資料下載

參數(shù)資料

| 型號(hào): | DAC1627D1G25 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | DAC |

| 中文描述: | PARALLEL, WORD INPUT LOADING, 0.02 us SETTLING TIME, 16-BIT DAC, PQCC72 |

| 封裝: | 10 X 10 MM, 0.85 MM HEIGHT, PLASTIC, SOT813-3, HVQFN-72 |

| 文件頁(yè)數(shù): | 22/69頁(yè) |

| 文件大?。?/td> | 1677K |

| 代理商: | DAC1627D1G25 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)

DAC1627D1G25

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2011. All rights reserved.

Objective data sheet

Rev. 1 — 29 April 2011

22 of 69

NXP Semiconductors

DAC1627D1G25

Dual 16-bit DAC: up to 1.25 Gsps; x2, x4 and x8 interpolating

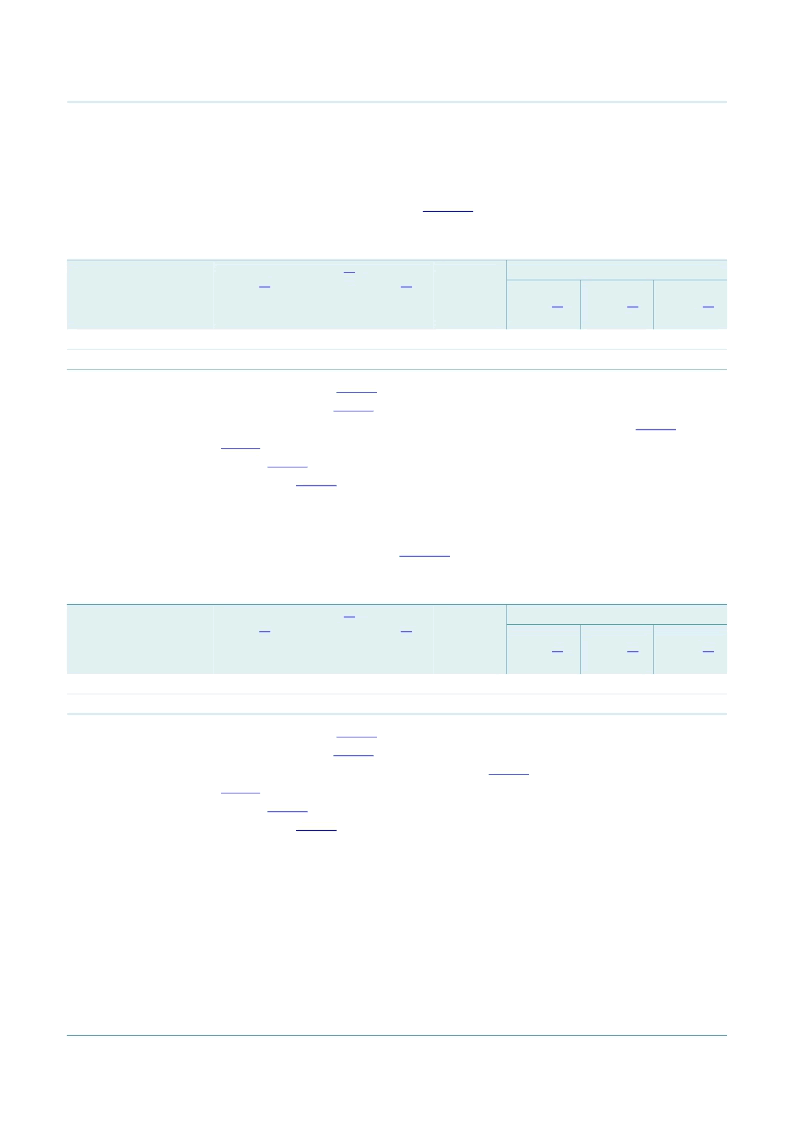

10.7.1

CDI mode 0 (x2 interpolation)

CDI mode 0 (

×

2 interpolation) is required when the value of the LVDS DDR clock is twice

the internal maximum CDI frequency.

Table 12

shows examples of applications using an

internal PLL or an external clock for the DAC core.

[1]

Bits CDI_MODE[1:0] of register MISC_CNTRL (see

Table 89

).

[2]

Bits INTERPOLATION[1:0] of register TXCFG (see

Table 25

).

[3]

If a Single Sideband Modulator (SSBM) is used, see bits NCO_ON and MODULATION[2:0] of register TXCFG (see

Table 25

).

[4]

Pins CLKP and CLKN (see

Figure 2

).

[5]

Bit PLL_PD of register PLLCFG (see

Table 26

).

[6]

Bits PLL_DIV[1:0] of register PLLCFG (see

Table 26

).

10.7.2

CDI mode 1 (x4 interpolation)

CDI mode 1 (

×

4 interpolation) is required when the values of the LVDS DDR clock and the

internal CDI frequency are equal.

Table 13

shows examples of applications using an

internal PLL or an external clock for the DAC core.

[1]

Bits CDI_MODE[1:0] of register MISC_CNTRL (see

Table 89

).

[2]

Bits INTERPOLATION[1:0] of register TXCFG (see

Table 25

).

[3]

If SSBM is used, see bits NCO_ON and MODULATION[2:0] of register TXCFG (see

Table 25

).

[4]

Pins CLKP and CLKN (see

Figure 2

).

[5]

Bit PLL_PD of register PLLCFG (see

Table 26

).

[6]

Bits PLL_DIV[1:0] of register PLLCFG (see

Table 26

).

Table 12.

LVDS DDR

rate (MHz)

CDI mode 0: operating modes examples

I rate;

Q rate

(Msps)

CDI

mode

[1]

FIR mode

[2]

SSBM

rate

[3]

(Msps)

DAC rate

(Msps)

PLL configuration

PLL

status

[5]

DAC input

clock

[4]

(MHz)

320

640

PLL

divider

[6]

320

320

320

320

0

0

×

2

×

2

640

640

640

640

enabled

disabled

2

n.a.

Table 13.

LVDS DDR

rate (MHz)

CDI mode 1: operating modes examples

I rate;

Q rate

(Msps)

CDI

mode

[1]

FIR mode

[2]

SSBM

rate

[3]

(Msps)

DAC rate

(Msps)

PLL configuration

PLL

status

[5]

DAC input

clock

[4]

(MHz)

250

1000

PLL

divider

[6]

250

250

250

250

1

1

×

4

×

4

1000

1000

1000

1000

enabled

disabled

4

n.a.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DAC1627D1G25HN | Dual 16-bit DAC, up to 1.25 Gsps; 2x 4x and 8x interpolating |

| DAN2222E | SWITCHING DIODE |

| DCX100NS | 100mA DUAL COMPLEMENTARY PRE-BIASED TRANSISTORS |

| DCX100NS-7 | 100mA DUAL COMPLEMENTARY PRE-BIASED TRANSISTORS |

| DCX114EH-7 | COMPLEMENTARY NPN/PNP PRE-BIASED SMALL SIGNAL SOT-563 DUAL SURFACE MOUNT TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DAC1627D1G25/DB,598 | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開(kāi)發(fā)工具 DAC DEMOBOARD RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類型:ADC 工具用于評(píng)估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| DAC1627D1G25HN/C1, | 功能描述:調(diào)節(jié)器/解調(diào)器 DUAL 16b 1.25GSPS to 1.25 Gsps RoHS:否 制造商:Texas Instruments 封裝 / 箱體:PVQFN-N24 封裝:Reel |

| DAC1627D1G25HN/C1,551 | 功能描述:調(diào)節(jié)器/解調(diào)器 Dual 16-bit DAC, up to 1.25 Gsps RoHS:否 制造商:Texas Instruments 封裝 / 箱體:PVQFN-N24 封裝:Reel |

| DAC1627D1G25HN-C1 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。