- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369679 > CYNCP80192 Network Processing PDF資料下載

參數(shù)資料

| 型號(hào): | CYNCP80192 |

| 英文描述: | Network Processing |

| 中文描述: | 網(wǎng)絡(luò)處理 |

| 文件頁(yè)數(shù): | 22/42頁(yè) |

| 文件大小: | 679K |

| 代理商: | CYNCP80192 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)

CYNCP80192

Document #: 38-02043 Rev. *B

Page 22 of 42

Index

. This field contains index returned by the NSEs where a successful hit was found. This field is valid only if the hit bit in the

Result Register 0 is a 1.

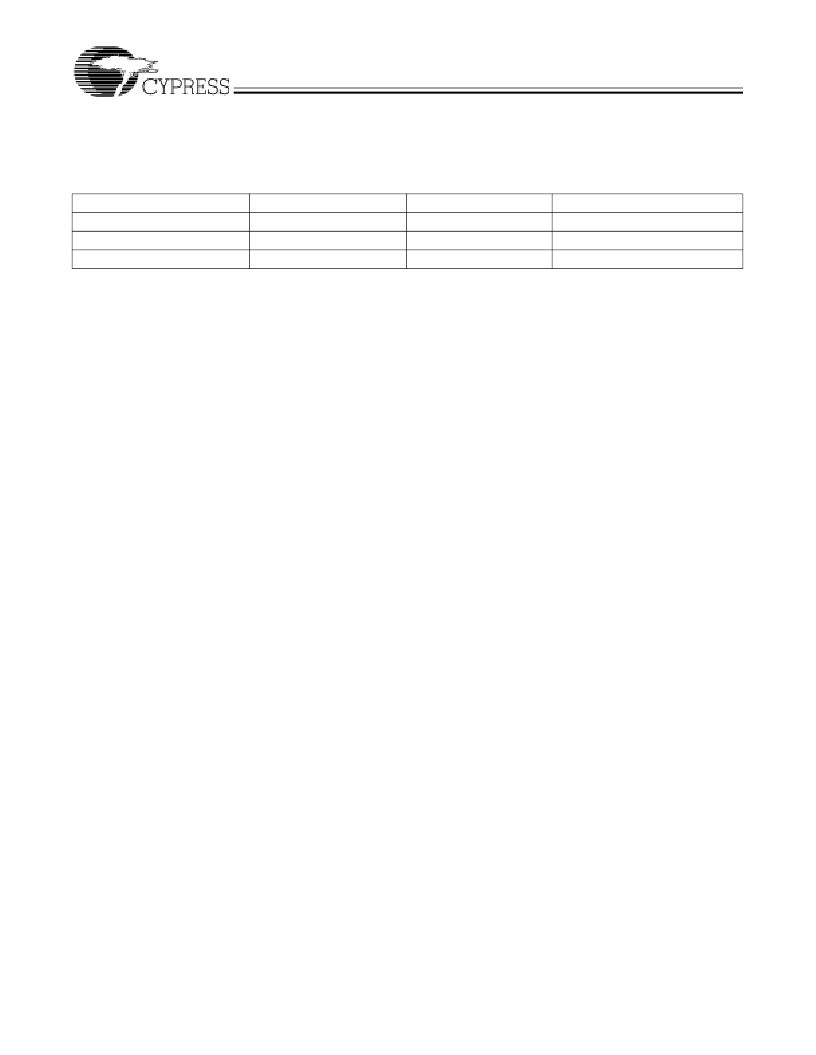

Table 7-19

below shows the number of index bits for various NSEs.

Note

. CYNSE70032 and

CYNSE70064 bits 23–22 of the index will always be 00. (Refer to the specifications of the CYNSE70XXX for the description of

the index returned by the NSEs.)

Note

. SAP is the SSRAM Address (SADR) Prefix. These bits are passed along with the command descriptor word in the SAP field.

7.3.8

The network processor(s) can Write up to 32 contexts. There can be up to 32 operations in flight through the database copro-

cessing subsystem. If 30 descriptor entries are in use, the NDC will issue the DESC_AFUL signal to inform that command

descriptor ring is almost full. The database coprocessor continually executes the commands posted in the descriptors. The

commands are executed and the results written in the Result Registers 0 and 1 of the corresponding descriptor entries. The

network processor(s) will Read the results and free the descriptor entry for another command.

The handshake for the command handoff from the network processor uses the start bit in the command descriptor. The network

processor will load the command and the associative parameter along with the start bit in the descriptors. As the start bit in

a descriptor is set, the NDC will take the command and insert it in the pipeline queue for execution. The commands in the pipeline

queue are strictly handled in a first-in, first-out manner.

Note

. The network processor must make sure that the start bit is set in

the last access to the descriptor to complete the command.

The commands from the pipeline queue are continually executed by the NDC and the results are loaded back to the command

initiating descriptor’s Result Registers 0 and 1. The handshake for the results from the NDC back to network processor is done

through any of the following mechanisms:

Done bit

CPID bus, STRB signal.

In the first method, after the network processor has issued a command to the NDC, the network processor will continually poll

that command descriptor entry for the done bit. Once done bit is set, it signals to the network processor that the results are Ready

in Results Registers 0 and 1 for Readout. Reading of these registers by the network processor will clear the done bit. This

descriptor entry is free and may now be used for another command.

In the second method, the network processor uses the interrupt mechanism for Reading the command results. After the results

are Ready in Result Registers 0 and 1 and the done bit is set, the NDC will assert pins CPID[7:0] (with the concatenated processor

and context ID information) and activate the STRB signal for one CLK cycle. This STRB signal interrupts and the CPID identifies

the context and/or processor for which the result are Ready. The context within that processor can wake up and Read the results

(Result Register 0 and 1) from the appropriate descriptor. Reading of these registers by the network processor will reset the done

bit. This descriptor entry is free and may now be used for another command.

Functional Overview of Context Descriptor

Table 7-19. Index Bits for NSEs

Device

CYNSE70032

CYNSE70064

CYNSE70128

SAP

21:19

21:20

23:21

SEID

18:14

19:15

20:16

Index

13:0

14:0

15:0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CYNSE70032 | Network Processing |

| CYNSE70128 | Network Processing |

| CYNSE70256 | Network Processing |

| CZET101 | Clock Driver |

| CZEU101 | Quad Peripheral Driver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYNPC80192-BGC | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:Network Database Coprocessor |

| CYNSE10128 | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:Ayama⑩ 10000 Network Search Engine |

| CYNSE10128-083FGCI | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:Ayama⑩ 10000 Network Search Engine |

| CYNSE10128-100FGC | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:Ayama⑩ 10000 Network Search Engine |

| CYNSE10128-133FGC | 制造商:CYPRESS 制造商全稱(chēng):Cypress Semiconductor 功能描述:Ayama⑩ 10000 Network Search Engine |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。