- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4293 > XC3S200A-4VQ100I (Xilinx Inc)IC FPGA SPARTAN 3 100VQFP PDF資料下載

參數(shù)資料

| 型號: | XC3S200A-4VQ100I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 78/132頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN 3 100VQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3A |

| LAB/CLB數(shù): | 448 |

| 邏輯元件/單元數(shù): | 4032 |

| RAM 位總計(jì): | 294912 |

| 輸入/輸出數(shù): | 68 |

| 門數(shù): | 200000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁當(dāng)前第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁

Introduction and Ordering Information

DS529-1 (v2.0) August 19, 2010

5

Configuration

Spartan-3A FPGAs are programmed by loading

configuration data into robust, reprogrammable, static

CMOS configuration latches (CCLs) that collectively control

all functional elements and routing resources. The FPGA’s

configuration data is stored externally in a PROM or some

other non-volatile medium, either on or off the board. After

applying power, the configuration data is written to the

FPGA using any of seven different modes:

Master Serial from a Xilinx Platform Flash PROM

Serial Peripheral Interface (SPI) from an

industry-standard SPI serial Flash

Byte Peripheral Interface (BPI) Up from an

industry-standard x8 or x8/x16 parallel NOR Flash

Slave Serial, typically downloaded from a processor

Slave Parallel, typically downloaded from a processor

Boundary Scan (JTAG), typically downloaded from a

processor or system tester

Furthermore, Spartan-3A FPGAs support MultiBoot

configuration, allowing two or more FPGA configuration

bitstreams to be stored in a single SPI serial Flash or a BPI

parallel NOR Flash. The FPGA application controls which

configuration to load next and when to load it.

Additionally, each Spartan-3A FPGA contains a unique,

factory-programmed Device DNA identifier useful for

tracking purposes, anti-cloning designs, or IP protection.

I/O Capabilities

The Spartan-3A FPGA SelectIO interface supports many

popular single-ended and differential standards. Table 2

shows the number of user I/Os as well as the number of

differential I/O pairs available for each device/package

combination. Some of the user I/Os are unidirectional

input-only pins as indicated in Table 2.

Spartan-3A FPGAs support the following single-ended

standards:

3.3V low-voltage TTL (LVTTL)

Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V,

1.5V, or 1.2V

3.3V PCI at 33 MHz or 66 MHz

HSTL I, II, and III at 1.5V and 1.8V, commonly used in

memory applications

SSTL I and II at 1.8V, 2.5V, and 3.3V, commonly used

for memory applications

Spartan-3A FPGAs support the following differential

standards:

LVDS, mini-LVDS, RSDS, and PPDS I/O at 2.5V or

3.3V

Bus LVDS I/O at 2.5V

TMDS I/O at 3.3V

Differential HSTL and SSTL I/O

LVPECL inputs at 2.5V or 3.3V

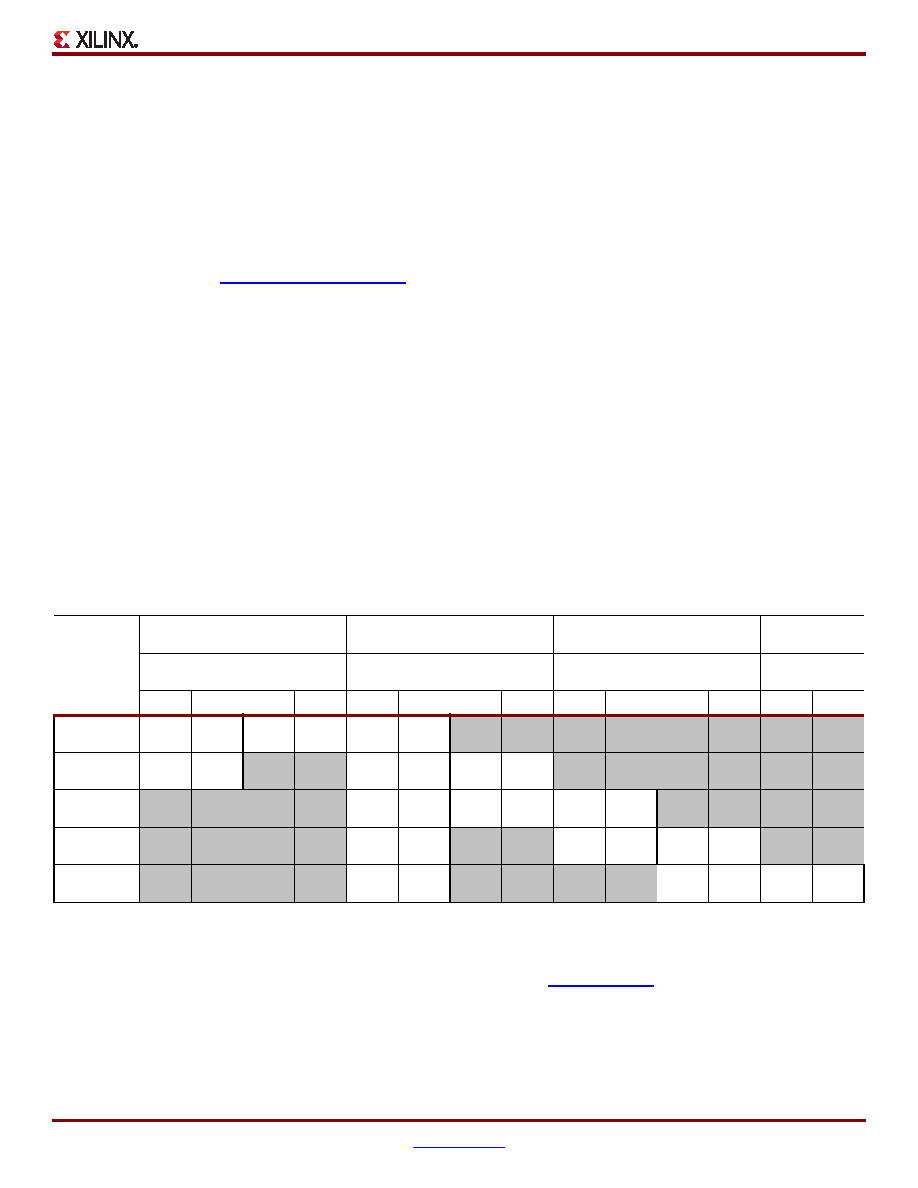

Table 2: Available User I/Os and Differential (Diff) I/O Pairs

Package

VQ100

VQG100

TQ144

TQG144

FT256

FTG256

FG320

FGG320

FG400

FGG400

FG484

FGG484

FG676

FGG676

Body Size

(mm)

14 x 14(2)

20 x 20(2)

17 x 17

19 x 19

21 x 21

23 x 23

27 x 27

Device

User

Diff

User

Diff

User

Diff

User

Diff

User

Diff

User

Diff

User

Diff

XC3S50A

68

(13)

60

(24)

108

(7)

50

(24)

144

(32)

64

(32)

-

XC3S200A

68

(13)

60

(24)

-

195

(35)

90

(50)

248

(56)

112

(64)

-

XC3S400A

-

195

(35)

90

(50)

251

(59)

112

(64)

311

(63)

142

(78)

-

XC3S700A

-

161

(13)

74

(36)

-

311

(63)

142

(78)

372

(84)

165

(93)

-

XC3S1400A

-

161

(13)

74

(36)

-

375

(87)

165

(93)

502

(94)

227

(131)

Notes:

1.

The number shown in bold indicates the maximum number of I/O and input-only pins. The number shown in (italics) indicates the number

of input-only pins. The differential (Diff) input-only pin count includes both differential pairs on input-only pins and differential pairs on I/O pins

within I/O banks that are restricted to differential inputs.

2.

The footprints for the VQ/TQ packages are larger than the package body. See the Package Drawings for details.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3S100E-4TQ144I | IC FPGA SPARTAN 3E 144TQFP |

| XC3S100E-5TQG144C | IC FPGA SPARTAN-3E 100K 144-TQFP |

| XC3S100E-5CPG132C | IC FPGA SPARTAN-3E 100K 132CSBGA |

| XC3S100E-4CPG132I | IC FPGA SPARTAN-3E 100K 132CSBGA |

| 24LC16B-E/ST | IC EEPROM 16KBIT 400KHZ 8TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S200A-4VQG100C | 功能描述:IC FPGA SPARTAN-3A 200K 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3A 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S200A-4VQG100I | 功能描述:IC FPGA SPARTAN-3A 200K 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3A 標(biāo)準(zhǔn)包裝:24 系列:ECP2 LAB/CLB數(shù):1500 邏輯元件/單元數(shù):12000 RAM 位總計(jì):226304 輸入/輸出數(shù):131 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) |

| XC3S200A-5FG320C | 功能描述:IC SPARTAN-3A FPGA 200K 320FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3A 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S200A-5FGG320C | 功能描述:IC SPARTAN-3A FPGA 200K 320-FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3A 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S200A-5FT256C | 功能描述:IC SPARTAN-3A FPGA 200K 256FTBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3A 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。