- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98143 > ST52E430B/D (STMICROELECTRONICS) 8-BIT, UVPROM, 20 MHz, MICROCONTROLLER, CDIP32 PDF資料下載

參數(shù)資料

| 型號(hào): | ST52E430B/D |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, UVPROM, 20 MHz, MICROCONTROLLER, CDIP32 |

| 封裝: | WINDOWED, SHRINK, CERAMIC, DIP-32 |

| 文件頁(yè)數(shù): | 47/120頁(yè) |

| 文件大小: | 502K |

| 代理商: | ST52E430B/D |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)當(dāng)前第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

32/120

ST52T430/E430

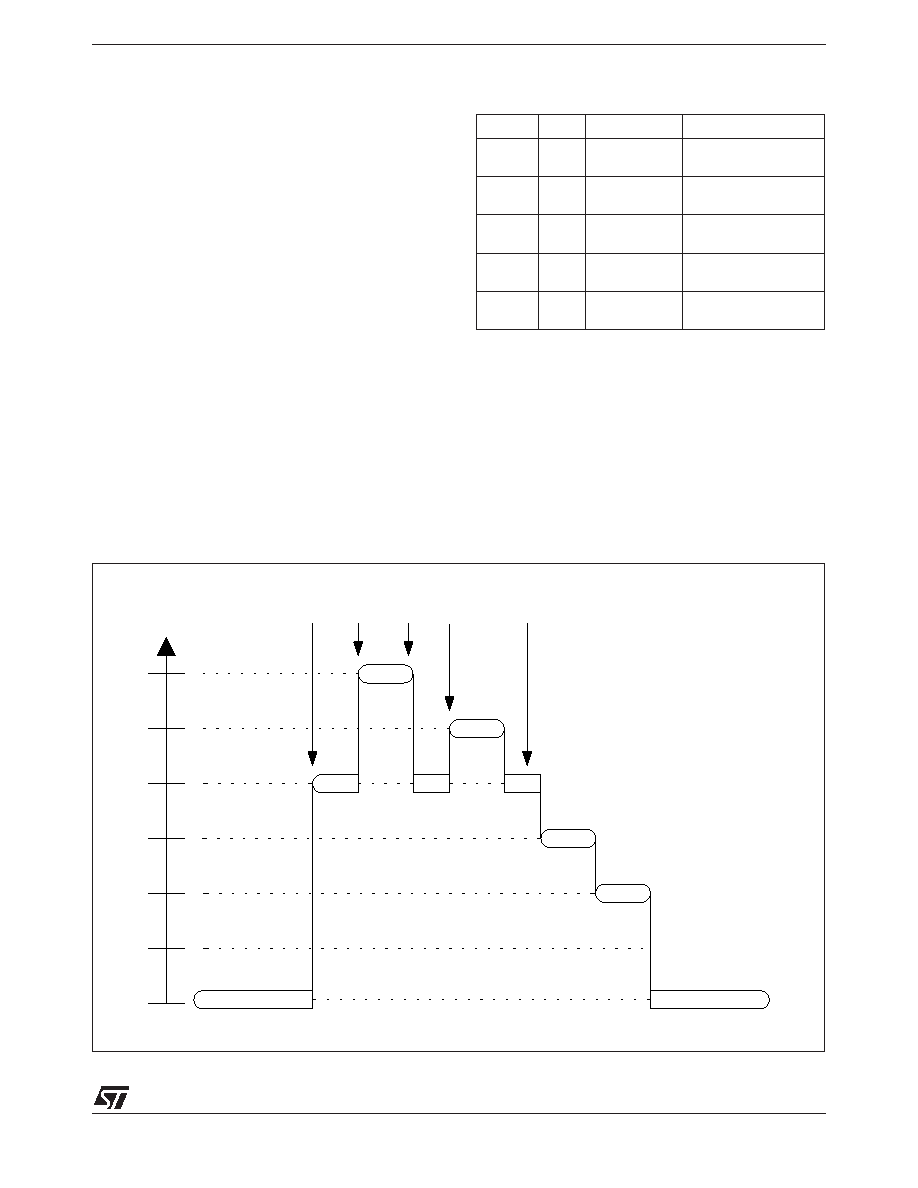

4.5 Interrupt Priority

Seven priority levels are available: level 6 has the

lowest priority, level 0 has the highest priority.

Level 6 is associated to the Main Program, levels 5

to 1 are programmable by means of the priority

registers called REG_CONF17 and REG_CONF18

(see fig.4.5 and table 4.3); whereas the higher level

is related to the external interrupt (INT_EXT).

PWM/Timers, UART and ADC are identified by a

three-bits Peripheral Code (see Table 4.2); in order

to set the i-th priority level the user must write the

peripheral label i in the related INTi priority level.

i.e.

LDRC

10,

193

//(load

the

value

193=’11000001’ in the RAM Register 10)

LDRC

11,

168

//(load

the

value

168=’10101000’ in the RAM Register 11)

LDCR 17, 10

// set

the REG_CONF17=

‘11000001’

LDCR 18, 11

// set

the REG_CONF18=

‘10101000’

thus defining the following priority levels:

Bit

Name

Value

Level

0, 1,2

INT1

Peripheral

Code

High

3, 4,5

INT2

Peripheral

Code

Medium-High

6,7,8

INT3

Peripheral

Code

Medium-Low

9,10,11 INT4

Peripheral

Code

Low

12,13,14 INT5

Peripheral

Code

Very Low

Table 4.3. Conf. Register 17&18 Description

MAIN PROGRAM

5

4

3

2

1

0

INT2

INT0

INT2

INT1

INT2

INT3

INT4

MAIN PROGRAM

PRIORITY

LEVEL

INT2

INT0

INT4

INT1

INT3

6

Figure 4.6. Example of a Sequence of Interrupt Requests

n

Level 1: INT_PWM/TIMER0 (PWM/TIMER 0

Code: 001)

n

Level 2: INT_ADC (ADC Code: 000)

n

Level 3:INT_PWM/TIMER2 (PWM/TIMER 2

Code: 011)

n

Level 4: INT_UART (UART Code: 100)

n

Level 5: INT_PWM/TIMER1 (PWM/TIMER 1

Code: 010)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST52F510F1M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO20 |

| ST52F510G0B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 |

| ST52F513F0M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO20 |

| ST52F513F1B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP20 |

| ST52F513G1M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST52E430K1B6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K1M6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K1T6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K2B6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K2M6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。