- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384797 > OR4E4 (Lineage Power) Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) PDF資料下載

參數(shù)資料

| 型號: | OR4E4 |

| 廠商: | Lineage Power |

| 英文描述: | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| 中文描述: | 現(xiàn)場可編程門陣列(現(xiàn)場可編程門陣列) |

| 文件頁數(shù): | 28/132頁 |

| 文件大?。?/td> | 2667K |

| 代理商: | OR4E4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁

28

Lucent Technologies Inc.

Preliminary Data Sheet

August 2000

ORCA Series 4 FPGAs

Embedded Block RAM

(continued)

CAM Mode

The CAM block is a content address memory that pro-

vides fast address searches by receiving data input

and returning addresses that contain the data. Imple-

mented in each EBR are two 16-word x 8-bit CAM

function blocks.

The CAM has three modes: single match, multiple

match, and clear, which are all achieved in one clock

cycle. In single-match mode, an 8-bit data input is inter-

nally decoded and reports a match when data is

present in a particular RAM address. Its result is

reported by a corresponding single address bit. In mul-

tiple match, the same occurs with the exception of mul-

tiple address lines report the match. Clear mode is

used to clear the CAM contents in one clock cycle by

erasing all locations.)

Arbitration logic is optionally programmed by the user

to signal occurrences of data collisions as well as to

block both ports from writing at the same time. The

arbitration logic prioritizes PORT1. When utilizing the

arbiter, the signal BUSY indicates data is being written

to PORT1. This BUSY output signals PORT1 activity by

driving a high output. The arbitration default is enabled;

however, the user may disable the arbiter in configura-

tion. If the arbiter is turned off, both ports could be writ-

ten at the same time and the data would be corrupt. In

this scenario, the BUSY signal will indicate a possible

error.

There is also a user option which dedicates PORT 1 to

communications to the system bus. In this mode the

user logic only has access to PORT0 and arbitration

logic is enabled. The system bus utilizes the priority

given to it by the arbiter; therefore, the system bus will

always be able to write to the EBR.

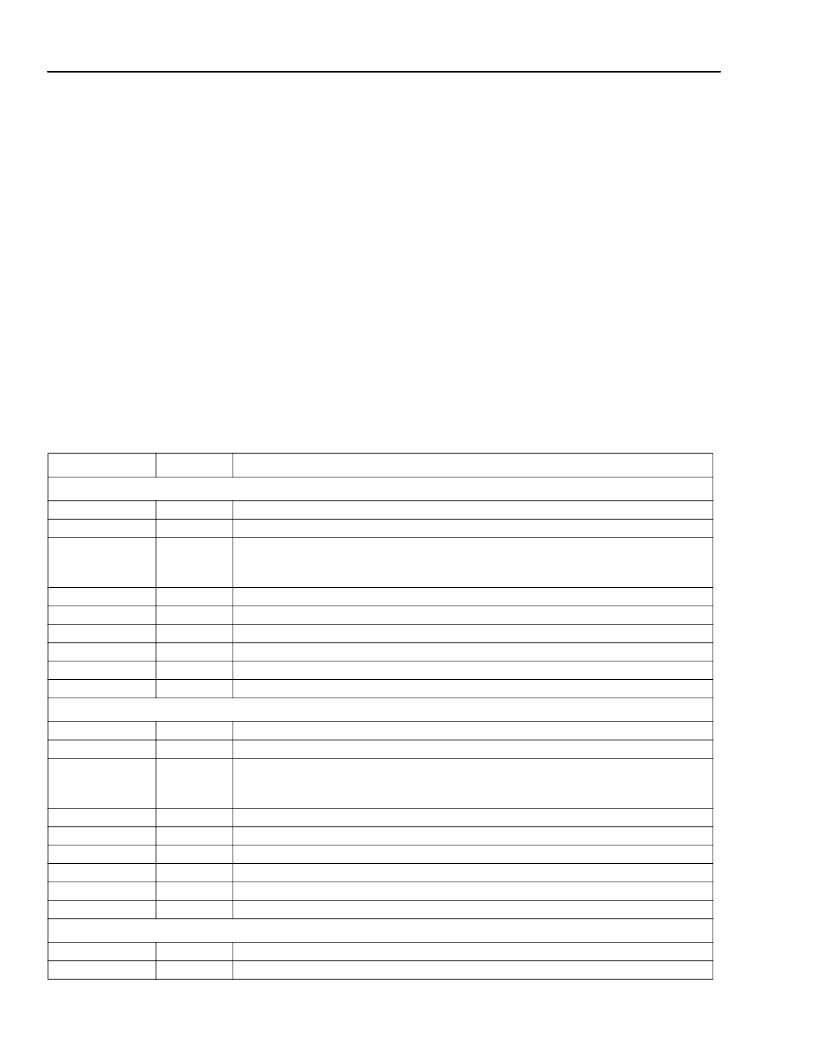

Table 9. RAM Signals

Port Signals

I/O

Function

PORT 0

AR0[#:0]

AW0[#:0]

BW0<1:0>

I

I

I

Address to be read.

Address to be written.

Byte-write enable.

Byte = 8 bits + parity bit.

<1> = bits[17, 15:9] <0> = bits[16, 7:0]

Positive-edge asynchronous read clock.

Positive-edge synchronous write clock.

Enables read to output. Active-high.

Enables write to occur. Active-high.

Input data to be written to RAM.

Output data of memory contents at referenced address.

CKR0

CKW0

CSR0

CSW0

D [#:0]

Q [#:0]

I

I

I

I

I

O

PORT 1

AR1[#:0]

AW1[#:0]

BW1<1:0>

I

I

I

Address to be read.

Address to be written.

Byte-write enable.

Byte = 8 bits + parity bit.

<1> = bits[17, 15:9] <0> = bits[16, 7:0]

Positive-edge asynchronous read clock.

Positive-edge synchronous write clock.

Enables read to output. Active-high.

Enables write to occur. Active-high.

Input data to be written to RAM.

Output data of memory contents at referenced address.

CKR1

CKW1

CSR1

CSW1

D [#:0]

Q [#:0]

I

I

I

I

I

O

Control

BUSY

RESET

O

I

PORT1 writing. Active-high.

Data output registers cleared. Memory contents unaffected. Active-low.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR4E6 | Field-Programmable Gate Arrays(現(xiàn)場可編程門陣列) |

| ORT4622 | Field-Programmable System Chip (FPSC) Four Channel x 622 Mbits/s Backplane Transceiver(現(xiàn)場可編程系統(tǒng)芯片(四通道x 622 M位/秒背板收發(fā)器)) |

| ORT8850 | Field-Programmable System Chip(現(xiàn)場可編程系統(tǒng)芯片) |

| OS8740230 | Si Optical Receiver, 40 - 870MHz, 225mA max. @ 24VDC |

| OSC-1A0 | Ultra Miniature TCXO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR4E4-1BA352 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E4-1BA416 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E4-1BC432 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E4-1BM680 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| OR4E4-2BA352 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。