- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376976 > DS3112N RECT BRIDGE GPP 15A 600V GBJ PDF資料下載

參數(shù)資料

| 型號: | DS3112N |

| 英文描述: | RECT BRIDGE GPP 15A 600V GBJ |

| 中文描述: | 坦佩化T3/E3復用器3.3化T3/E3成幀器和M13/E13/G.747復用器 |

| 文件頁數(shù): | 101/135頁 |

| 文件大小: | 585K |

| 代理商: | DS3112N |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁當前第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁

DS3112

101 of 135

Bits 0 to 5/Transmit FEAC Code Word A Data (TFCA0 to TFCA5).

The FEAC code word is of the

form ...0xxxxxx011111111... where the rightmost bit is transmitted first. These six bits are the middle six

bits of the second byte of the FEAC code word (i.e., the six “x” bits). The device can generate two

different code words and these six bits represent what will be transmitted for code word A. TFCA0 is the

LSB and is transmitted first while TFCA5 is the MSB and is transmitted last. The TFS0 and TFS1 control

bits determine if this code word is to be generated. These bits should only be changed when the transmit

FEAC controller is in the idle state (TFS0 = 0 and TFS1 = 0).

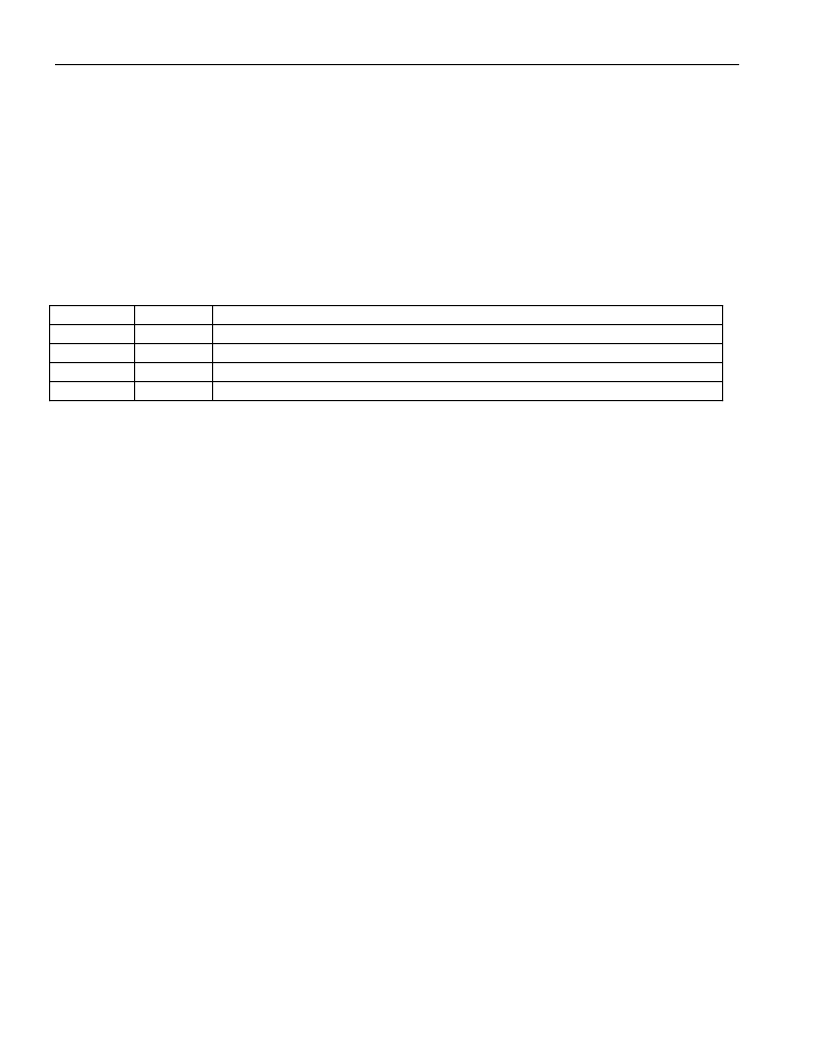

Bits 6 and 7/Transmit FEAC Code Word Select Bits 0 and 1 (TFS0 and TFS1).

These two bits

control what two available code words should be generated. Both TFS0 and TFS1 are edge triggered. To

change the action, the host must go back to the null state (TFS0 = TFS1 = 0) before proceeding to the

desired action. Wait a minimum of (10) code words before changing to out-of-idle state.

TFS1

TFS0

0

0

Idle state; do not generate a FEAC code word (send all ones)

0

1

Send 10 of code word A followed by all ones

1

0

Send 10 of code word A followed by 10 of code word B followed by all ones

1

1

Send code word A continuously (will be sent for at least 10 times)

Bits 8 to 13/Transmit FEAC Code Word B Data (TFCB0 to TFCB5).

The FEAC code word is of the

form ...0xxxxxx011111111... where the rightmost bit is transmitted first. These six bits are the middle six

bits of the second byte of the FEAC code word (i.e., the six “x” bits). The device can generate two

different code words and these six bits represent what will be transmitted for code word B. TFCB0 is the

LSB and is transmitted first while TFCB5 is the MSB and is transmitted last. The TFS0 and TFS1 control

bits determine if this code word is to be generated. These bits should only be changed when the transmit

FEAC controller is in the idle state (TFS0 = 0 and TFS1 = 0).

Bit 14/Interrupt Enable, Receive FEAC Idle (IERFI).

This bit masks or enables interrupts caused by

the Receive FEAC Idle (RFI) bit in the FSR register.

0 = interrupt masked

1 = interrupt unmasked

Bit 15/Receive FEAC Controller Reset (RFR).

A zero to one transition will reset the receive FEAC

controller and flush the Receive FEAC FIFO. This bit must be cleared and set again for a subsequent

reset.

ACTION

相關PDF資料 |

PDF描述 |

|---|---|

| DS3112RD | RECT BRIDGE GPP 15A 800V GBJ |

| DS3134 | Chateau Channelized T1 And E1 And HDLC Controller |

| DS3160 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| DS3171 | Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers |

| DS3171N | Single/Dual/Triple/Quad DS3/E3 Single-Chip Transceivers |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3112N+ | 功能描述:網(wǎng)絡控制器與處理器 IC TEMPE T3/E3 MUX FRMR & M13/E13/G.747 MUX RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3112N+W | 功能描述:網(wǎng)絡控制器與處理器 IC TEMPE T3/E3 MUX FRMR & M13/E13/G.747 MUX RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3112NC1 | 制造商:Maxim Integrated Products 功能描述:T3 E3 MULTIPLEXER, 3.3V T3/E3 FRAMER AND M13/E13/G.747 MUX - Rail/Tube |

| DS3112ND1E | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS3112RD | 功能描述:網(wǎng)絡控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。