- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384065 > μPD45128441 (NEC Corp.) 128M-bit Synchronous DRAM(128M 同步DRAM) PDF資料下載

參數(shù)資料

| 型號: | μPD45128441 |

| 廠商: | NEC Corp. |

| 英文描述: | 128M-bit Synchronous DRAM(128M 同步DRAM) |

| 中文描述: | 128兆位同步DRAM(128M的同步DRAM)的 |

| 文件頁數(shù): | 35/84頁 |

| 文件大小: | 693K |

| 代理商: | ΜPD45128441 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

Preliminary Data Sheet

35

μ

PD45128441, 45128841, 45128163

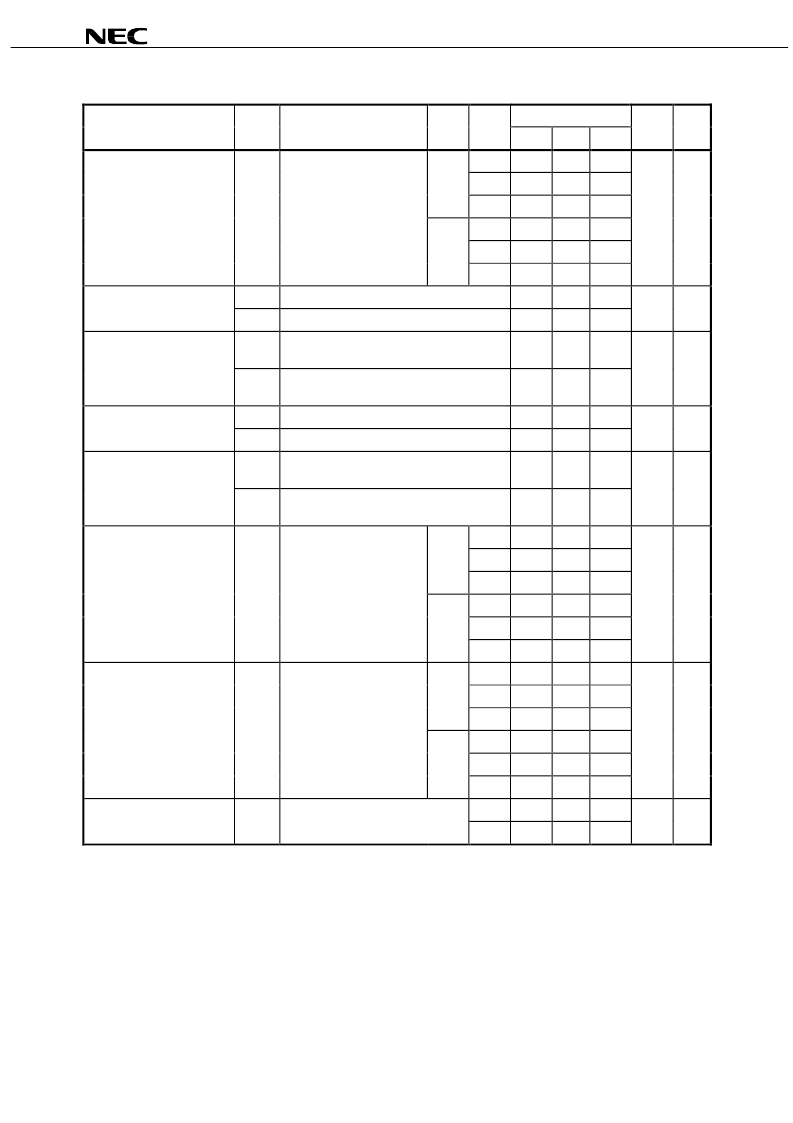

DC Characteristics 1 (Recommended Operating Conditions unless otherwise noted)

Parameter

Symbol

Test condition

/CAS

Grade

Maximum

Unit

Notes

latency

×

4

×

8

×

16

Operating current

I

CC1

Burst length = 1,

CL = 2

-A80

110

120

135

mA

1

t

RC

≥

t

RC (MIN.)

, Io = 0 mA,

-A10

95

105

120

One bank active

-A10B

90

100

110

CL = 3

-A80

115

125

150

-A10

100

110

130

-A10B

95

105

120

Precharge standby current

I

CC2

P

CKE

≤

V

IL (MAX.)

, t

CK

= 15 ns

1

1

1

mA

in power down mode

I

CC2

PS

CKE

≤

V

IL (MAX.)

, t

CK

=

∞

0.5

0.5

0.5

Precharge standby current

in non power down mode

I

CC2

N

CKE

≥

V

IH (MIN.)

, t

CK

= 15 ns, /CS

≥

V

IH (MIN.)

,

Input signals are changed one time during 30 ns.

20

20

20

mA

I

CC2

NS

CKE

≥

V

IH (MIN.)

, t

CK

=

∞

,

Input signals are stable.

6

6

6

Active standby current

I

CC3

P

CKE

≤

V

IL (MAX.)

, t

CK

= 15 ns

5

5

5

mA

in power down mode

I

CC3

PS

CKE

≤

V

IL (MAX.)

, t

CK

=

∞

4

4

4

Active standby current

in non power down mode

I

CC3

N

CKE

≥

V

IH (MIN.)

, t

CK

= 15 ns, /CS

≥

V

IH (MIN.)

,

Input signals are changed one time during 30 ns.

25

25

25

mA

I

CC3

NS

CKE

≥

V

IH (MIN.)

, t

CK

=

∞

,

Input signals are stable.

12

12

15

Operating current

I

CC4

t

CK

≥

t

CK (MIN.)

, Io = 0 mA,

CL = 2

-A80

100

115

165

mA

2

(Burst mode)

All banks active

-A10

80

90

130

-A10B

75

80

120

CL = 3

-A80

115

135

195

-A10

100

115

165

-A10B

95

105

150

Refresh current

I

CC5

t

RC

≥

t

RC (MIN.)

CL = 2

-A80

260

260

260

mA

3

-A10

240

240

240

-A10B

220

220

220

CL = 3

-A80

270

270

270

-A10

250

250

250

-A10B

230

230

230

Self refresh current

I

CC6

CKE

≤

0.2 V

-**

2

2

2

mA

-**L

0.8

0.8

0.8

Notes 1.

I

CC1

depends on output loading and cycle rates. Specified values are obtained with the output open. In

addition to this, I

CC1

is measured condition that addresses are changed only one time during t

CK (MIN.)

.

2.

I

CC4

depends on output loading and cycle rates. Specified values are obtained with the output open. In

addition to this, I

CC4

is measured condition that addresses are changed only one time during t

CK (MIN.)

.

3.

I

CC5

is measured on condition that addresses are changed only one time during t

CK (MIN.)

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD4516161A | 16M-bit Synchronous DRAM(16M 同步動(dòng)態(tài)RAM) |

| μPD4516421A | 16M-bit Synchronous DRAM(16M 同步動(dòng)態(tài)RAM) |

| μPD4516821A | 16M-bit Synchronous DRAM(16M 同步動(dòng)態(tài)RAM) |

| μPD45256163 | 256M-Bit Synchronous DRAM(256M 同步 動(dòng)態(tài)RAM) |

| μPD45256441 | 256M-Bit Synchronous DRAM(256M 同步 動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD45128441G5 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M-bit Synchronous DRAM 4-bank, LVTTL WTR (Wide Temperature Range) |

| PD45128441G5-A10I-9JF | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M-bit Synchronous DRAM 4-bank, LVTTL WTR (Wide Temperature Range) |

| PD45128441G5-A10LI-9JF | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M-bit Synchronous DRAM 4-bank, LVTTL WTR (Wide Temperature Range) |

| PD45128441G5-A10LT-9JF | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M-bit Synchronous DRAM 4-bank, LVTTL WTR (Wide Temperature Range) |

| PD45128441G5-A10T-9JF | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M-bit Synchronous DRAM 4-bank, LVTTL WTR (Wide Temperature Range) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。