- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1977 > XRT86VX38IB329-F (Exar Corporation)IC TI/E1/J1 FRAMER/LIU 329FPBGA PDF資料下載

參數(shù)資料

| 型號: | XRT86VX38IB329-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 31/61頁 |

| 文件大小: | 0K |

| 描述: | IC TI/E1/J1 FRAMER/LIU 329FPBGA |

| 標準包裝: | 90 |

| 控制器類型: | T1/E1/J1 調(diào)幀器,LIU |

| 電源電壓: | 3.3V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 329-FBGA |

| 供應(yīng)商設(shè)備封裝: | 329-FPBGA(17x17) |

| 包裝: | 散裝 |

| 其它名稱: | 1016-1439 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

XRT86VX38

34

REV. 1.0.3

OCTAL T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

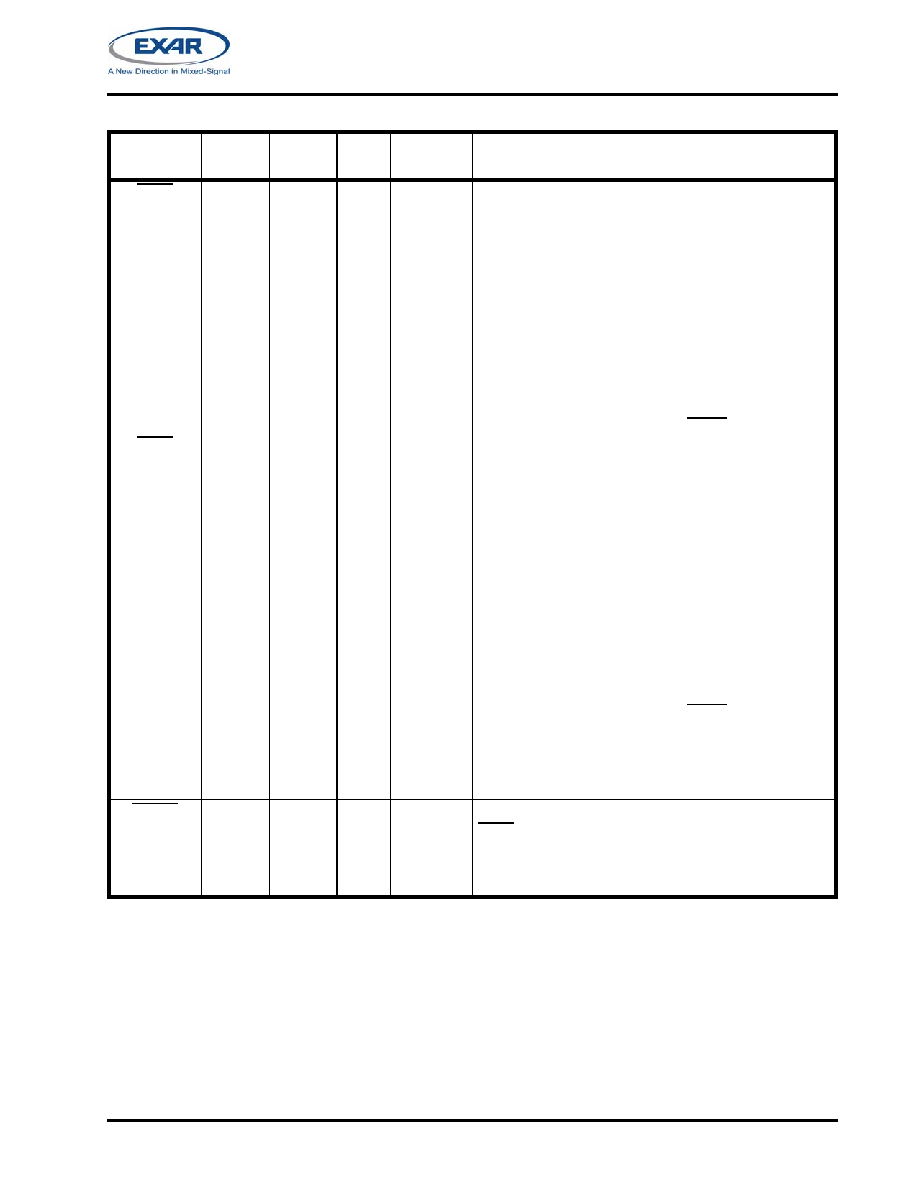

ACK0

ACK1

T18

R19

N15

M15

I-

DMA Cycle Acknowledge Input—DMA Controller 0

(Write):

The external DMA Controller will assert this input pin “Low”

when the following two conditions are met:

1. After the DMA Controller, within the Framer has

asserted (toggled “Low”), the Req_0 output signal.

2. When the external DMA Controller is ready to

transfer data from external memory to the selected

Transmit HDLC buffer.

At this point, the DMA transfer between the external mem-

ory and the selected Transmit HDLC buffer may begin.

After completion of the DMA cycle, the external DMA Con-

troller will negate this input pin after the DMA Controller

within the Framer has negated the Req_0 output pin. The

external DMA Controller must do this in order to acknowl-

edge the end of the DMA cycle.

DMA Cycle Acknowledge Input—DMA Controller 1

(Read):

The external DMA Controller asserts this input pin “Low”

when the following two conditions are met:

1. After the DMA Controller, within the Framer has

asserted (toggled "Low"), the Req_1 output signal.

2. When the external DMA Controller is ready to

transfer data from the selected Receive HDLC buffer

to external memory.

At this point, the DMA transfer between the selected

Receive HDLC buffer and the external memory may begin.

After completion of the DMA cycle, the external DMA Con-

troller will negate this input pin after the DMA Controller

within the Framer has negated the Req_1 output pin. The

external DMA Controller will do this in order to acknowl-

edge the end of the DMA cycle.

NOTE:

This pin is internally pulled “High” with a 50k

resistor.

RESET

V4

R4

I

-

Hardware Reset Input

Reset is an active low input. If this pin is pulled “Low” for

more than 10

S, the device will be reset. When this occurs,

all output will be ‘tri-stated’, and all internal registers will be

reset to their default values.

MICROPROCESSOR INTERFACE

SIGNAL NAME

329 PKG

BALL#

256 PKG

BALL #

TYPE

OUTPUT

DRIVE (MA)

DESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT94L31IB-L | IC MAPPER DS3/E3/STS-1 504TBGA |

| XRT94L33IB-L | IC MAPPER DS3/E3/STS-1 504TBGA |

| XRT94L43IB-F | IC MAPPER SONET/SDH OC12 516BGA |

| XS1-G02B-FB144-I4 | IC MCU 32BIT 16KB OTP 144FBGA |

| XTR114U/2K5 | IC 4-20MA I-TRANSMITTER 14-SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L30 | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30_0611 | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30_10 | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS12-STM4 OR STS3-STM1 SONET-SDH Transceiver |

| XRT91L306 | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30ES | 功能描述:總線收發(fā)器 RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。