- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4265 > XC3S1400AN-5FGG484C (Xilinx Inc)IC FPGA SPARTAN-3AN 484FPGA PDF資料下載

參數(shù)資料

| 型號: | XC3S1400AN-5FGG484C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 37/123頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3AN 484FPGA |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 2816 |

| 邏輯元件/單元數(shù): | 25344 |

| RAM 位總計: | 589824 |

| 輸入/輸出數(shù): | 372 |

| 門數(shù): | 1400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 484-BBGA |

| 供應(yīng)商設(shè)備封裝: | 484-FBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁

Spartan-3AN FPGA Family: DC and Switching Characteristics

DS557 (v4.1) April 1, 2011

Product Specification

20

Differential Output Pairs

DIFF_SSTL3_II(8)

3.0

3.3

3.6

100

–

–1.1

–1.9

Notes:

1.

The VCCO rails supply only differential output drivers, not input circuits.

2.

VICM must be less than VCCAUX.

3.

These true differential output standards are supported only on FPGA banks 0 and 2. Inputs are unrestricted. See the “Using I/O Resources”

chapter in UG331.

4.

5.

LVPECL is supported on inputs only, not outputs. Requires VCCAUX = 3.3V ± 10%.

6.

LVPECL_33 maximum VICM =VCCAUX –(VID / 2)

7.

Requires VCCAUX = 3.3V ± 10% for inputs. (VCCAUX – 300 mV) VICM (VCCAUX – 37 mV)

8.

VREF inputs are used for the DIFF_SSTL and DIFF_HSTL standards. The VREF settings are the same as for the single-ended versions in

9.

These higher-drive output standards are supported only on FPGA banks 1 and 3. Inputs are unrestricted. See the “Using I/O Resources”

chapter in UG331.

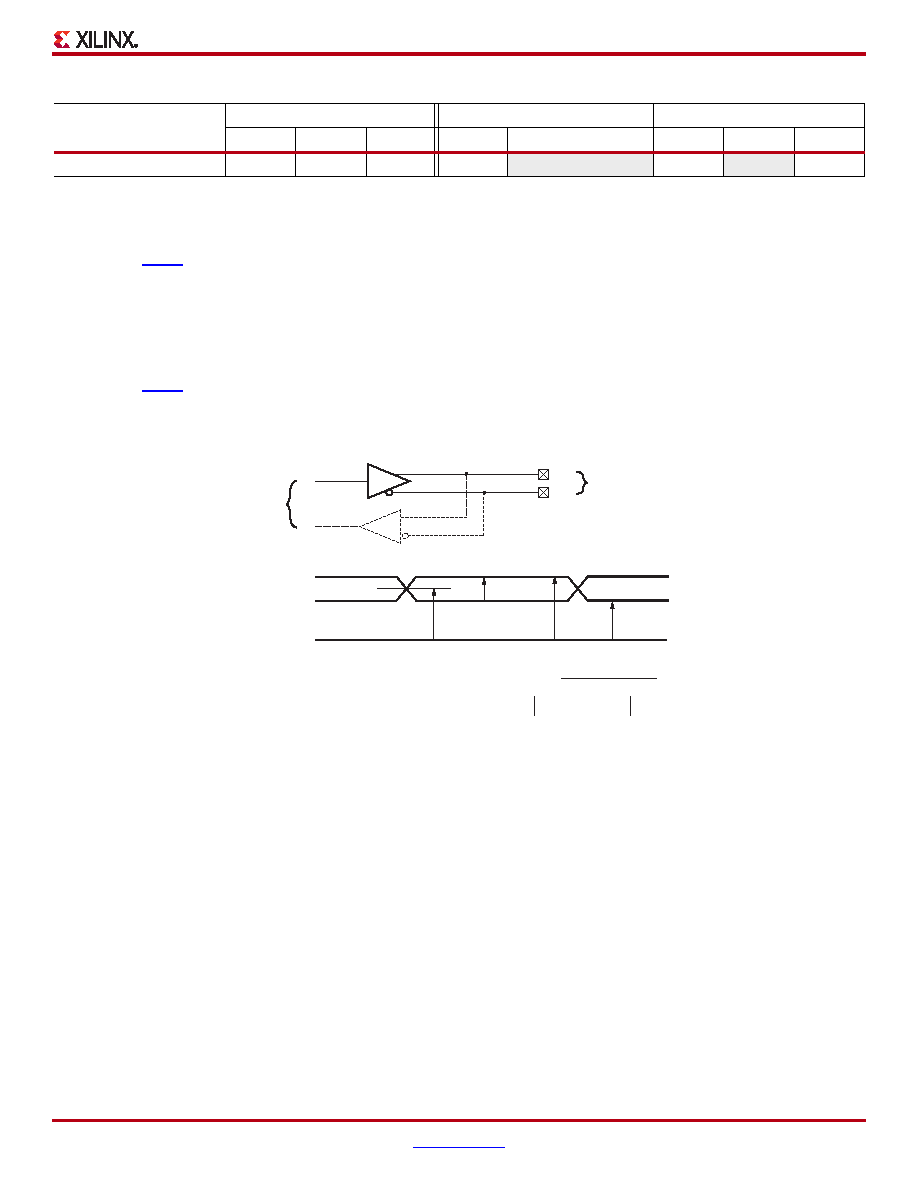

X-Ref Target - Figure 7

Figure 7: Differential Output Voltages

Table 15: Recommended Operating Conditions for User I/Os Using Differential Signal Standards (Cont’d)

IOSTANDARD Attribute

VCCO for Drivers(1)

VID

VICM(2)

Min (V)

Nom (V)

Max (V)

Min (mV)

Nom (mV) Max (mV)

Min (V)

Nom (V)

Max (V)

V

OUTN

V

OUTP

GND level

50%

V

OCM

V

OCM

V

OD

V

OL

V

OH

V

OUTP

Internal

Logic

V

OUTN

N

P

= Output common mode voltage =

2

V

OUTP +VOUTN

V

OD = Output differential voltage =

V

OH = Output voltage indicating a High logic level

V

OL

= Output voltage indicating a Low logic level

V

OUTP -VOUTN

Differential

I/O Pair Pins

DS529-3_11_082810

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 25AA080DT-I/MNY | IC SRL EEPROM 1KX8 1.8V 8-TDFN |

| 3344-38 | SCREW BRDLOCK M2.5 0.31" 1=1PC |

| XCV50E-7PQ240C | IC FPGA 1.8V 71K GATES 240-PQFP |

| 25AA080CT-I/MNY | IC SRL EEPROM 1KX8 1.8V 8-TDFN |

| 3344-26 | SCREW BRDLOCK M2.6 0.31" 1=1PC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S1400AN-5FGG676C | 功能描述:IC FPGA SPARTAN -3N1400K 676FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3AN 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計:221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC3S1500 | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1500-4CP132C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1500-4CP132I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1500-4CPG132C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA Family: Complete Data Sheet |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。