- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225535 > W9412G6CH-5 (WINBOND ELECTRONICS CORP) 8M X 16 DDR DRAM, 0.7 ns, PDSO66 PDF資料下載

參數(shù)資料

| 型號: | W9412G6CH-5 |

| 廠商: | WINBOND ELECTRONICS CORP |

| 元件分類: | DRAM |

| 英文描述: | 8M X 16 DDR DRAM, 0.7 ns, PDSO66 |

| 封裝: | 0.400 INCH, 0.65 MM PITCH, ROHS COMPLIANT, TSOP2-66 |

| 文件頁數(shù): | 21/55頁 |

| 文件大小: | 2011K |

| 代理商: | W9412G6CH-5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

W9412G6CH

Publication Release Date:Nov. 19, 2007

- 28 -

Revision A07

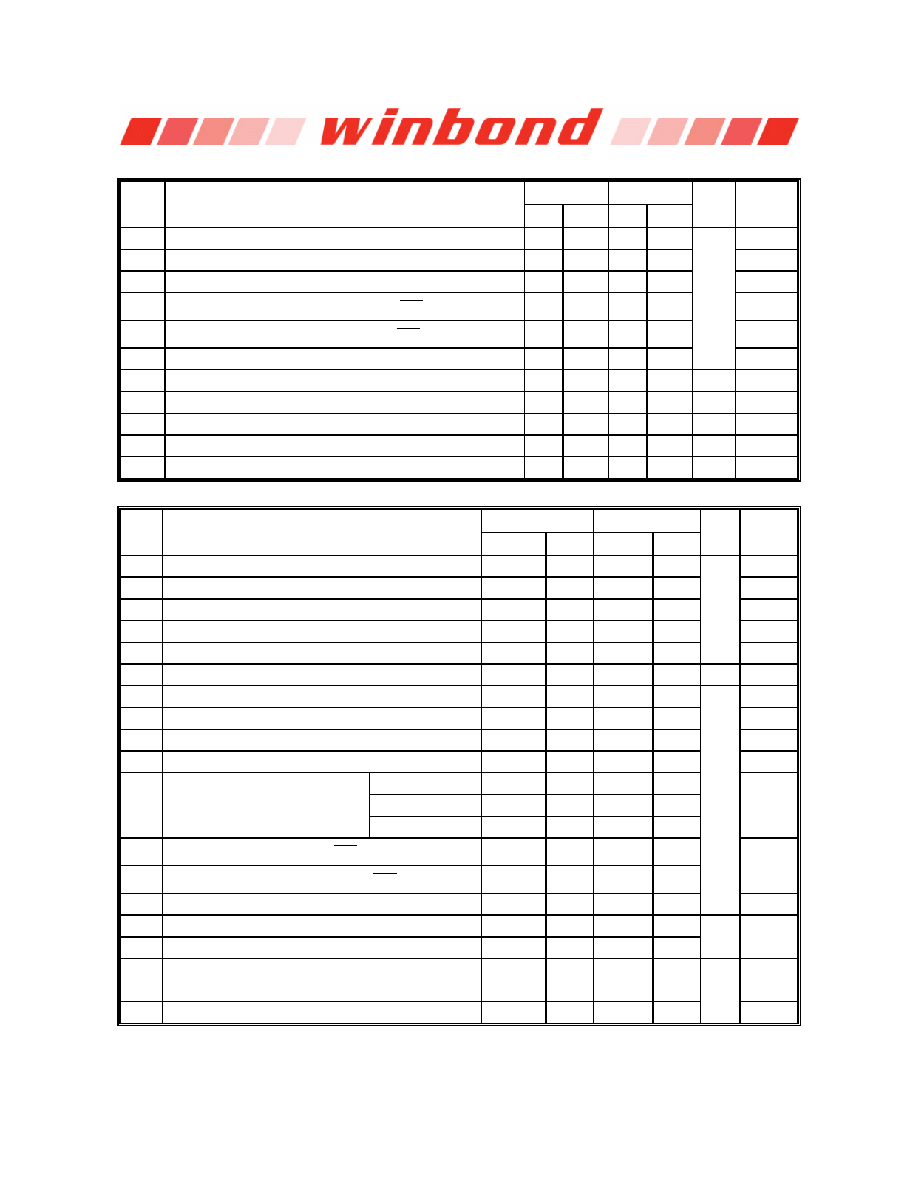

AC Characteristics and Operating Condition, continued

-45

-5

SYM.

PARAMETER

MIN. MAX. MIN. MAX.

UNIT NOTES

tIS

Input Setup Time

0.75

0.8

tIH

Input Hold Time

0.75

0.8

tIPW

Control & Address Input Pulse Width (for each input)

2.2

tHZ

Data-out High-impedance Time from CLK, CLK

-0.7

0.7

-0.7

0.7

tLZ

Data-out Low-impedance Time from CLK, CLK

-0.7

0.7

-0.7

0.7

tT(SS)

SSTL Input Transition

0.5

1.5

0.5

1.5

nS

tWTR

Internal Write to Read Command Delay

2

1

tCK

tXSNR

Exit Self Refresh to non-Read Command

72

75

nS

tXSRD

Exit Self Refresh to Read Command

200

tCK

tREFI

Refresh Interval Time (4k / 64mS)

15.6

S

17

tMRD

Mode Register Set Cycle Time

9

10

nS

-6

-75

SYM.

PARAMETER

MIN.

MAX.

MIN.

MAX.

UNIT NOTES

tRC

Active to Ref/Active Command Period

54

60

tRFC

Ref to Ref/Active Command Period

70

tRAS

Active to Precharge Command Period

42

100000

45

120000

tRCD

Active to Read/Write Command Delay Time

18

20

tRAP

Active to Read with Auto-precharge Enable

18

20

nS

tCCD

Read/Write(a) to Read/Write(b) Command Period

1

tCK

tRP

Precharge to Active Command Period

18

20

tRRD

Active(a) to Active(b) Command Period

12

15

tWR

Write Recovery Time

15

tDAL

Auto-precharge Write Recovery + Precharge Time

-

18

CL = 2

7.5

12

7.5

12

CL = 2.5

6

12

7.5

12

tCK

CLK Cycle Time

CL = 3

6

12

7.5

12

tAC

Data Access Time from CLK, CLK

-0.7

0.7

-0.75

0.75

tDQSCK DQS Output Access Time from CLK, CLK

-0.6

0.6

-0.75

0.75

16

tDQSQ

Data Strobe Edge to Output Data Edge Skew

0.4

0.5

nS

tCH

CLk High Level Width

0.45

0.55

0.45

0.55

tCL

CLK Low Level Width

0.45

0.55

0.45

0.55

tCK

11

tHP

CLK Half Period (minimum of actual Tch, Tcl)

min,

(tCL,TCH)

Min.

(tCL,tCH)

tQH

DQ Output Data Hold Time from DQS

tHP-0.5

tHP-0.75

nS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W942504CH-7 | 64M X 4 DDR DRAM, 0.75 ns, PDSO66 |

| W9864G6IH-6 | 4M X 16 DDR DRAM, 5 ns, PDSO54 |

| WA-1RX33-A4 | SNAP ACTING/LIMIT SWITCH |

| WA-A325CBM | Peripheral Interface |

| WA-A325CPC | Peripheral Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W9412G6IH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:2M × 4 BANKS × 16 BITS DDR SDRAM |

| W9412G6IH-5 | 功能描述:IC DDR-400 SDRAM 128MB 66TSSOPII RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 格式 - 存儲器:EEPROMs - 串行 存儲器類型:EEPROM 存儲容量:4K (512 x 8) 速度:400kHz 接口:I²C,2 線串口 電源電壓:2.7 V ~ 5.5 V 工作溫度:-40°C ~ 85°C 封裝/外殼:8-SOIC(0.173",4.40mm 寬) 供應(yīng)商設(shè)備封裝:8-MFP 包裝:帶卷 (TR) |

| W9412G6JH | 制造商:WINBOND 制造商全稱:Winbond 功能描述:2M ? 4 BANKS ? 16 BITS DDR SDRAM |

| W9412G6JH-4 | 制造商:Winbond Electronics Corp 功能描述:8*16B DDR1 制造商:Winbond Electronics Corp 功能描述:IC DDR SDRAM 128M 250MHZ 66TSOP |

| W9412G6JH-5 | 制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR SDRAM 128M-Bit 8Mx16 2.5V 66-Pin TSOP 制造商:Winbond Electronics Corp 功能描述:128M BIT DDR1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。