- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11744 > PI7C8150AMAE (Pericom)IC PCI-PCI BRIDGE 2PORT 208-FQFP PDF資料下載

參數(shù)資料

| 型號: | PI7C8150AMAE |

| 廠商: | Pericom |

| 文件頁數(shù): | 97/111頁 |

| 文件大小: | 0K |

| 描述: | IC PCI-PCI BRIDGE 2PORT 208-FQFP |

| 標準包裝: | 24 |

| 系列: | * |

| 應用: | * |

| 接口: | * |

| 電源電壓: | * |

| 封裝/外殼: | 208-BFQFP |

| 供應商設(shè)備封裝: | 208-FQFP(28x28) |

| 包裝: | 管件 |

| 安裝類型: | 表面貼裝 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁當前第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁

PI7C8150A

2-PORT PCI-TO-PCI BRIDGE

Page 86 of 111

APRIL 2006 – Revision 1.1

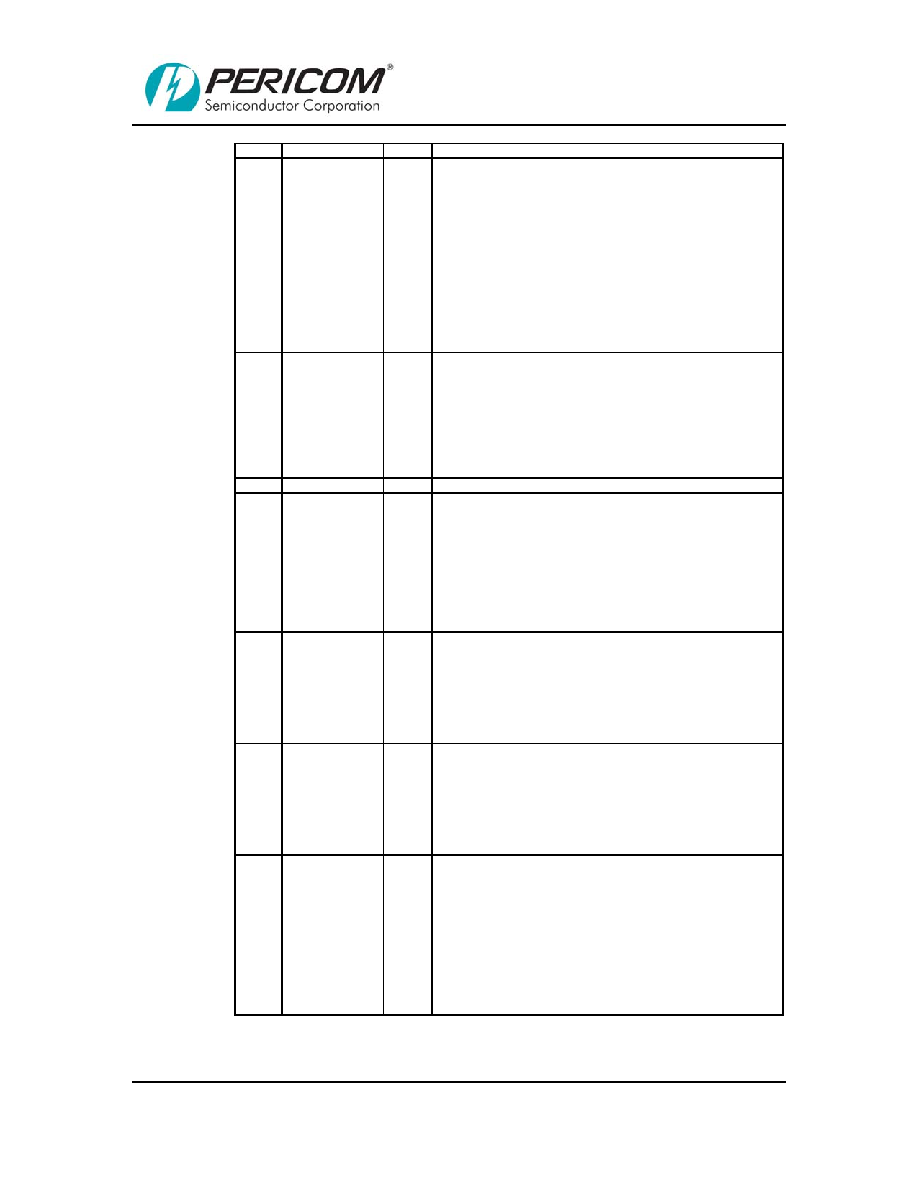

Bit

Function

Type

Description

18

ISA enable

R/W

Modifies the bridge’s response to ISA I/O addresses, applying only

to those addresses falling within the I/O base and limit address

registers and within the first 64KB or PCI I/O space.

0: forward all I/O addresses in the range defined by the I/O base and

I/O limit registers

1: blocks forwarding of ISA I/O addresses in the range defined by the

I/O base and I/O limit registers that are in the first 64KB of I/O space

that address the last 768 bytes in each 1KB block. Secondary I/O

transactions are forwarded upstream if the address falls within the

last 768 bytes in each 1KB block

Reset to 0

19

VGA enable

R/W

Controls the bridge’s response to VGA compatible addresses.

0: does not forward VGA compatible memory and I/O addresses

from primary to secondary

1: forward VGA compatible memory and I/O addresses from primary

to secondary regardless of other settings

Reset to 0

20

Reserved

R/O

Reserved. Returns 0 when read. Reset to 0

21

Master Abort

Mode

R/W

Control’s bridge’s behavior responding to master aborts on

secondary interface.

0: does not report master aborts (returns FFFF_FFFFh on reads and

discards data on writes)

1: reports master aborts by signaling target abort if possible by the

assertion of P_SERR_L if enabled

Reset to 0

22

Secondary

Interface Reset

R/W

Controls the assertion of S_RESET_L signal pin on the secondary

interface

0: does not force the assertion of S_RESET_L pin

1: forces the assertion of S_RESET_L

Reset to 0

23

Fast Back-to-

Back Enable

R/W

Controls bridge’s ability to generate fast back-to-back transactions to

different devices on the secondary interface.

0: does not allow fast back-to-back transactions

1: enables fast back-to-back transactions

Reset to 0

24

Primary Master

Timeout

R/W

Set’s the maximum number of PCI clocks the bridge will wait for an

initiator on the primary to repeat a delayed transaction request. The

counter starts right after the delayed transaction is at the front of the

queue. If the master has not repeated at least once before the counter

expires, the bridge discards the transaction from the queue.

0: 2

15

PCI clocks

1: 2

10

PCI clocks

Reset to 0

06-0057

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PIC18F2515-I/SP | IC MCU FLASH 24KX16 28-DIP |

| V300A15E500B2 | CONVERTER MOD DC/DC 15V 500W |

| PIC16C73B-04I/SO | IC MCU OTP 4KX14 A/D PWM 28SOIC |

| GRM1555C1H301JA01D | CAP CER 300PF 50V 5% NP0 0402 |

| PIC16LF876A-I/ML | IC PIC MCU FLASH 8KX14 28QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8150AMAE-33 | 功能描述:外圍驅(qū)動器與原件 - PCI 2 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8150AND | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:2-PORT PCI-to-PCI BRIDGE |

| PI7C8150AND-33 | 制造商:Pericom Semiconductor Corporation 功能描述:PCI-TO-PCI BRIDGE 256BGA - Rail/Tube |

| PI7C8150ANDE | 功能描述:外圍驅(qū)動器與原件 - PCI 2 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C8150B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | Asynchronous 2-Port PCI Bridge |

發(fā)布緊急采購,3分鐘左右您將得到回復。