- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382380 > PCD6003 (NXP Semiconductors N.V.) Digital telephone answering machine chip PDF資料下載

參數(shù)資料

| 型號: | PCD6003 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Digital telephone answering machine chip |

| 中文描述: | 數(shù)字電話應(yīng)答機(jī)芯片 |

| 文件頁數(shù): | 54/96頁 |

| 文件大?。?/td> | 385K |

| 代理商: | PCD6003 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當(dāng)前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

2001 Apr 17

54

Philips Semiconductors

Product specification

Digital telephone answering machine chip

PCD6003

The internal ROM fetching will be activated by making EA

a logic 1. If EA is logic 0 external program memory can be

connected and the internal ROM will be disabled. The

external memory interface block contains the MA and P2

generation logic and registers.

The P2 and MA latches have special enable signals.

Appropriate bits (MAGP and P2GP) in the control register

make P2 and MA available as general purpose output

ports or as the 80C51 address bus. The last option is

necessary for target debugging (EA = 0), external ROM

(EA = 0) or parallel flash memory (MAGP = 1 and

P2GP = 1). In these cases external latches must be

provided if the application needs the P2/MA as general

purpose output ports as well.

The MAGP and P2GP signals are bit 3 and 4 of the

configuration register latch. MA will be a general purpose

output port when MAGP is set to logic 0 by software

(default after reset). If MAGP is set to logic 1 the MA port

operates as the lower 8 bits of the program/data address

bus. P2 will be a general purpose output port when P2GP

is set to logic 0 by software (default after reset). If P2GP is

set to logic 1 the P2 port operates as the higher 8 bits of

the program/data address bus. The accessability of the

P2GP and MAGP bits of the ConfReg register in the

external interface block depends on the value of the EAM

(P4CFG.5) SFR bit: when EAM is logic 0 (default after

reset), the XRAM-mapped control registers can only be

accessed if P4.3 is logic 1 (compatible mode to PCD6002

DTAM device). Otherwise (i.e. when EAM is logic 0),

XRAM addressing is independent of the value of the P4.3

SFR bit, but needs ARD to be logic 0 (only available when

fetching from internal memory, i.e. EA is logic 1).

The latches are used for the configuration, MA and

P2 registers and they are mapped at addresses

200H to 202H of the external data memory map. Refer to

Table 48.

Register ConfReg (2-bit): this is the Configuration

Register. In this register single bits are set to control the

functionality of the external outputs. The content of this

register is given in Table 49. With the bits P2GP

(P2 General Purpose) and MAGP (MA General

Purpose) the output function of MA and P2 is

determined.

With bit P2GP = 0 (reset value) the output P2 is latched

and can be used as a general purpose output for

example to drive LEDs. Data can be written to the

register P2 with a MOVX command. With P2GP = 1 the

internal bus P2_int[7:0] is directly transferred to the

output P2[7:0]. This mode is for example applied when

using parallel flash. Output P2[7:0] delivers then the

high address byte for the parallel flash.

With MAGP = 0 (reset value MAGP = 0) the output

MA[7:0] can be used as a general purpose output.

Otherwise, output MA[7:0] serves as latch (with ALE as

enable signal) for the low address byte provided by a

internal bus.

Register MA (8-bit): If EA = 1 (internal ROM used) and

MAGP = 0 (default after reset) the MA pins will output

the contents of the MA register (0201H) which contains

00H after reset. The state of the MA pins can be

changed by writing a new value to the MA register. This

must be done with a MOVX instruction while the P4.3 bit

or the EAM bit is logic 1.

Register P2 (8-bit): If EA = 1 (internal ROM used) and

P2GP = 0 (default after reset) the P2 pins will output the

contents of the P2 register (0202H) which contains 00H

after reset. The state of the P2 pins can be changed by

writing a new value to the P2 register.This must be done

with a MOVX instruction while the P4.3 bit or the EAM

bit is logic 1.

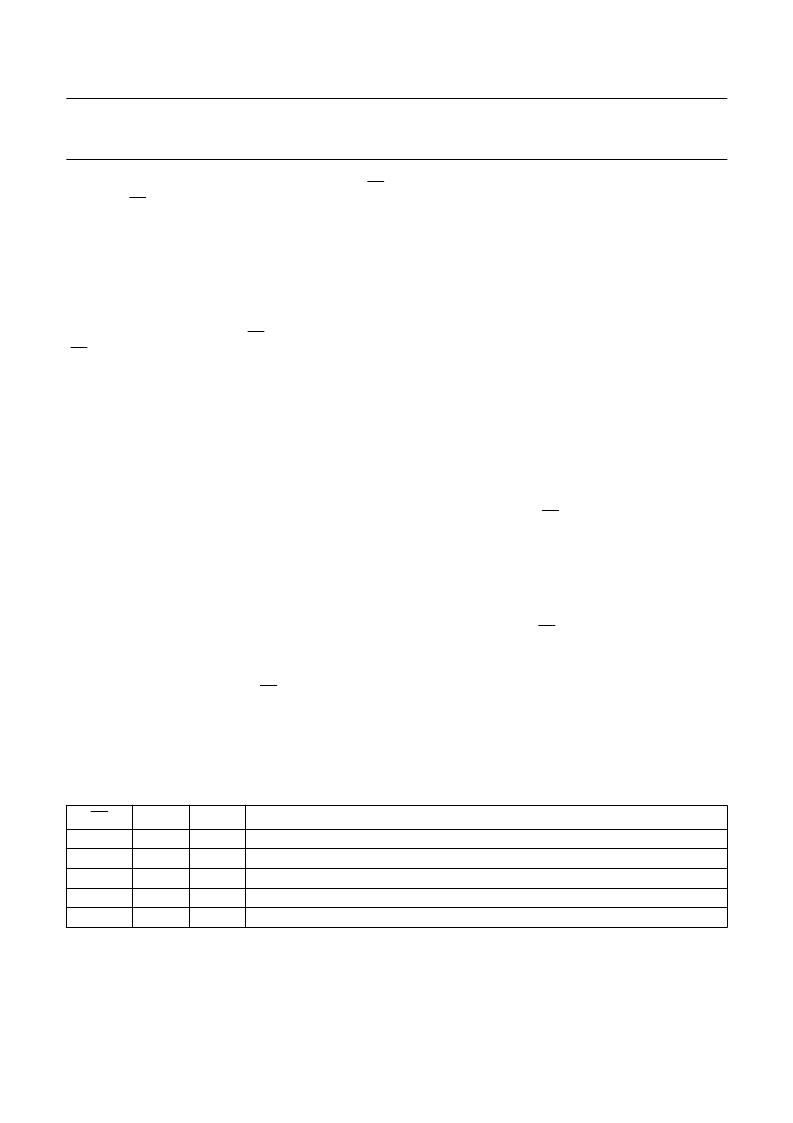

Table 47

Overview of P0/MA/P2 settings; notes 1, 2, 3, 4 and 5

Notes

1.

XA/XD: address and data during a MOVX instruction; PA/PD: address and data during a code fetch; GP: general

purpose port; low: low address byte; high: high address byte.

EA

MAGP

P2GP

FUNCTION P0/MA/P2

0

1

1

1

1

X

0

1

0

1

X

0

0

1

1

P0 = XA_low/XD/PA_low/PD, MA = XA/PA_low and P2 = XA/PA_high

P0 =XD, MA =GP and P2 = GP

P0 = XD, MA = XA_low and P2 = GP

P0 = XD, MA = GP and P2 = XA_high

P0 = XD, MA = XA_low and P2 = XA_high

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD6003H | Digital telephone answering machine chip |

| PCD6003U | Digital telephone answering machine chip |

| PCD8544 | 48 x 84 pixels matrix LCD controller/driver |

| PCD8544U | 48 x 84 pixels matrix LCD controller/driver |

| PCDAC12-4 | PC(ISA)BUS I/O CARD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD6003H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital telephone answering machine chip |

| PCD6003U | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Digital telephone answering machine chip |

| PCD-60-1050B | 制造商:Mean Well 功能描述:PCD-60 series 60 W 1050 mA 57 V Dimmable LED Driver Module 制造商:Mean Well 功能描述:AC to DC Power Supply Enclosed LED Single Output 34-57 Volts 制造商:Mean Well 功能描述:LED Drivers Power Supplies 59.85W 34-57V 1050mA CC Dimmable LED PS 制造商:Mean Well 功能描述:LED POWER SUPPLY 60W 90 - 135VAC OR 180 - 295VAC IN 500 - 2400MA SLCT CURRENT |

| PCD-60-1400B | 制造商:Mean Well 功能描述:AC to DC Power Supply Enclosed LED Single Output 25-43 Volts 制造商:Mean Well 功能描述:LED POWER SUPPLY 60W 90 - 135VAC OR 180 - 295VAC IN 500 - 2400MA SLCT CURRENT |

| PCD-60-1750B | 制造商:Mean Well 功能描述:AC to DC Power Supply Enclosed LED Single Output 20-34 Volts 制造商:Mean Well 功能描述:LED Drivers Power Supplies 59.5W 20-34V 1750mA CC Dimmable LED PS 制造商:Mean Well 功能描述:LED POWER SUPPLY 60W 90 - 135VAC OR 180 - 295VAC IN 500 - 2400MA SLCT CURRENT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。