- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC8240EC (Motorola, Inc.) Integrated Processor Hardware Specifications PDF資料下載

參數(shù)資料

| 型號: | MPC8240EC |

| 廠商: | Motorola, Inc. |

| 英文描述: | Integrated Processor Hardware Specifications |

| 中文描述: | 綜合處理器硬件規(guī)格 |

| 文件頁數(shù): | 17/52頁 |

| 文件大小: | 1027K |

| 代理商: | MPC8240EC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

MOTOROLA

MPC8240 Integrated Processor Hardware Specifications

For More Information On This Product,

Go to: www.freescale.com

17

Electrical and Thermal Characteristics

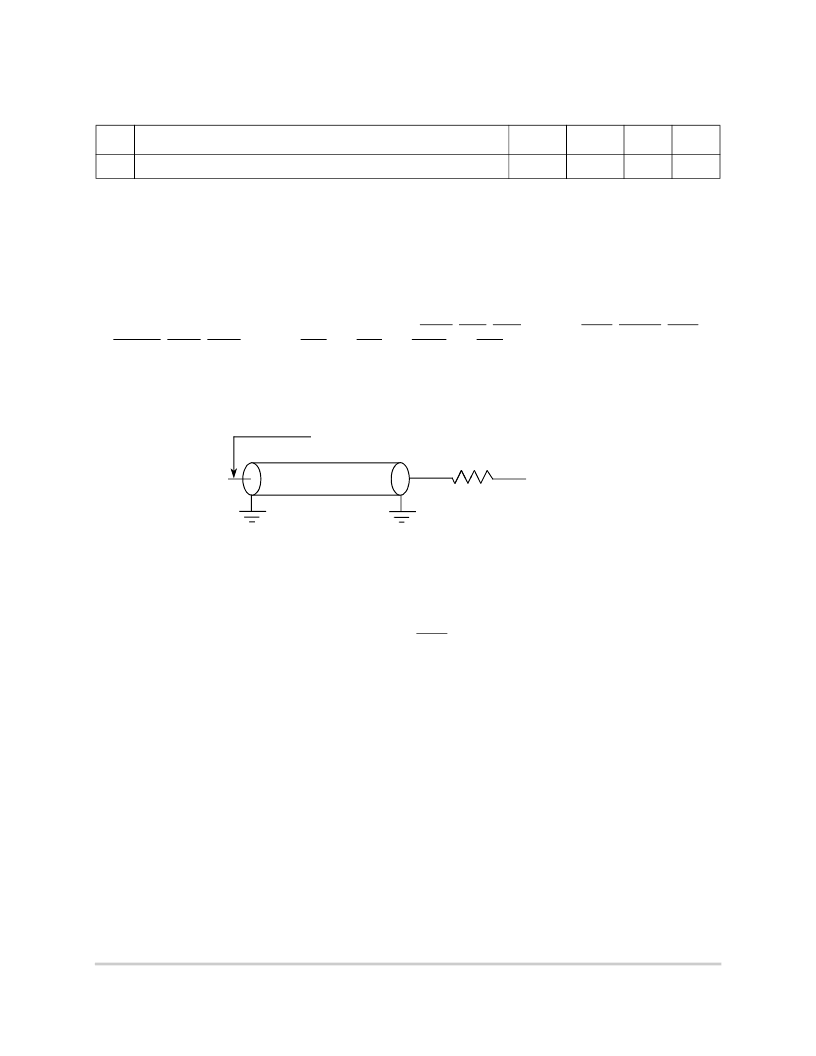

Figure 11. AC Test Load for the MPC8240

1.4.2.4.1

PCI Signal Output Hold Timing

In order to meet minimum output hold specifications relative to PCI_SYNC_IN for both 33- and 66-MHz

PCI systems, the MPC8240 has a programmable output hold delay for PCI signals. The initial value of the

output hold delay is determined by the values on the MCP and CKE reset configuration signals. Further

output hold delay values are available through programming the PCI_HOLD_DEL value of the PMCR2

configuration register.

14b

SDRAM_SYNC_IN to output high impedance (for all others)

—

4.0

ns

1

Notes:

1. All memory and related interface output signal specifications are specified from the VM = 1.4 V of the rising edge of

the memory bus clock, SDRAM_SYNC_IN to the TTL level (0.8 or 2.0 V) of the signal in question.

SDRAM_SYNC_IN is the same as PCI_SYNC_IN in 1:1 mode, but is twice the frequency in 2:1 mode

(processor/memory bus clock rising edges occur on every rising and falling edge of PCI_SYNC_IN). See Figure 8.

2. All PCI signals are measured from OV

DD

/2 of the rising edge of PCI_SYNC_IN to 0.285

×

OV

DD

or 0.615

×

OV

DD

of the signal in question for 3.3-V PCI signaling levels. See Figure 9.

3. All output timings assume a purely resistive 50-

load (see Figure 11). Output timings are measured at the pin;

time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

4. PCI bused signals are composed of the following signals: LOCK, IRDY, C/BE[0:3], PAR, TRDY, FRAME, STOP,

DEVSEL, PERR, SERR, AD[0:31], REQ[4:0], GNT[4:0], IDSEL, and INTA.

5. PCI hold times can be varied; see Section 1.4.2.4.1, “PCI Signal Output Hold Timing,” for information on

programmable PCI output hold times. The values shown for item 13a are for PCI compliance.

6. These specifications are for the default driver strengths indicated in Table 4.

Table 9. Output AC Timing Specifications (continued)

At recommended operating conditions (see Table 2) with LV

DD

= 3.3 V ± 0.3 V

Num

Characteristic

3, 6

Min

Max

Unit

Notes

Output

Z

0

= 50

OV

DD

/2 for PCI

GV

DD

/2 for Memory

R

L

= 50

Pin

Output Measurements are Made at the Device Pin

F

Freescale Semiconductor, Inc.

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC8240 | 32-Bit Microprocessor(32位微處理器) |

| MPC8260ACZU | MPC826xA (HiP4) Family Hardware Specifications |

| MPC8260CZU | MPC826xA (HiP4) Family Hardware Specifications |

| MPC8264ACZU | MPC826xA (HiP4) Family Hardware Specifications |

| MPC8264AZU | MPC826xA (HiP4) Family Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8241 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Intergrated Processor Hardware Specifications |

| MPC8241EC | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:MPC8241 Integrated Processor Hardware Specifications |

| MPC8241LVR166D | 功能描述:微處理器 - MPU INTEGRATED HOST PROC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8241LVR200D | 功能描述:微處理器 - MPU INTEGRATED HOST PROC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8241LVR266D | 功能描述:微處理器 - MPU INTEGRATED HOST PROC RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。