- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1022 Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-1022 |

| 英文描述: | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| 中文描述: | 低成本千兆速率發(fā)送/接收芯片組配備TTL的I / O |

| 文件頁(yè)數(shù): | 28/40頁(yè) |

| 文件大小: | 321K |

| 代理商: | HDMP-1022 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

643

Rx Operation Principles

The HDMP-1024 (Rx) is

monolithically implemented in a

high performance 25 GHz

f

t

bipolar process. When properly

configured, the Rx can accept

20B/24B CIMT line code frames,

and then output parallel 16B/17B/

20B/21B Data Word or 14B/18B

Control Word. The Rx provides

the following functions for link

operation:

Clock recovery

Frame synchronization

Data recovery

Demultiplexing

Frame decoding

Frame error detection

Link state control

Rx Encoding

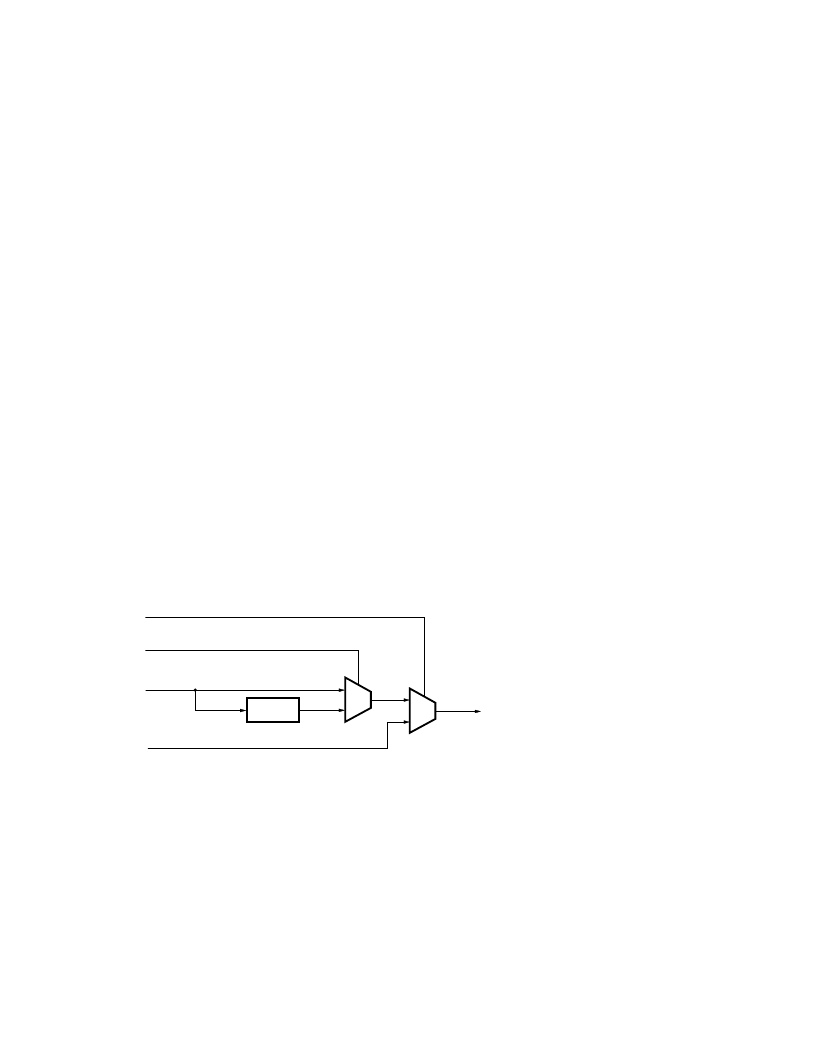

Figure 5 shows a simplified block

diagram of the receiver. The data

path consists of an Input Select,

an Input Sampler, a Frame

Demultiplexer, a Control Field (C-

Field) Decoder, and a Data Field

(D-Field) Decoder. An on-chip

phase-locked loop (PLL) is used

to extract timing reference from

the serial input (DIN or LIN). The

PLL includes a Phase-Frequency

Detector, a Loop Filter, and a

variable-frequency oscillator

(VCO). All the RX internal clock

signals are generated from a

Clock Generator. The Clock

Generator can be driven either by

internal VCO or external signal,

TCLK, depending on the Clock

Select configuration.

Integrated on the chip is a Link-

Control State Machine for link

status monitoring and link

startup. Figure 13 shows the

details of the Input Select. The

Input Select chooses either

nominal serial data (DIN) or

loopback (LIN) signal for the

Input Sampler’s input. If loopback

enable (LOOPEN) is asserted, the

LIN input is selected. Also

included in the Input Selector is

cable equalization circuitry. When

coaxial cable is used as the

transmission media, by setting

EQEN=1 (enable equalization),

the equalization circuitry is in the

DIN signal path and can

compensate for high-frequency

cable loss.

Because the Data Field of the

CIMT line code can be either

16-bit or 20-bit wide, the width

selection for Rx is made by

setting the input pin M20SEL

(Figure 5). If M20SEL=1, then

the Rx is configured to accept

serial input with 20-bit data field,

i.e., 24 bits per frame. If

M20SEL = 0, 16-bit data field is

selected.

Figure 13. HDMP-1024 (Rx) Input Selector.

CABLE EQ

1

0

EQEN

1

0

SIN

DIN

LIN

LOOPEN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價(jià)格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

| HDMP-1514 | Fibre Channel Receiver Chipset(光纖通道接收芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034A | 制造商:HP 制造商全稱:Agilent(Hewlett-Packard) 功能描述:Transmitter/Receiver Chip Set |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。