- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370499 > HDMP-1022 Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V PDF資料下載

參數(shù)資料

| 型號: | HDMP-1022 |

| 英文描述: | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| 中文描述: | 低成本千兆速率發(fā)送/接收芯片組配備TTL的I / O |

| 文件頁數(shù): | 11/40頁 |

| 文件大?。?/td> | 321K |

| 代理商: | HDMP-1022 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

626

HDMP-1022 (Tx), HDMP-1024 (Rx)

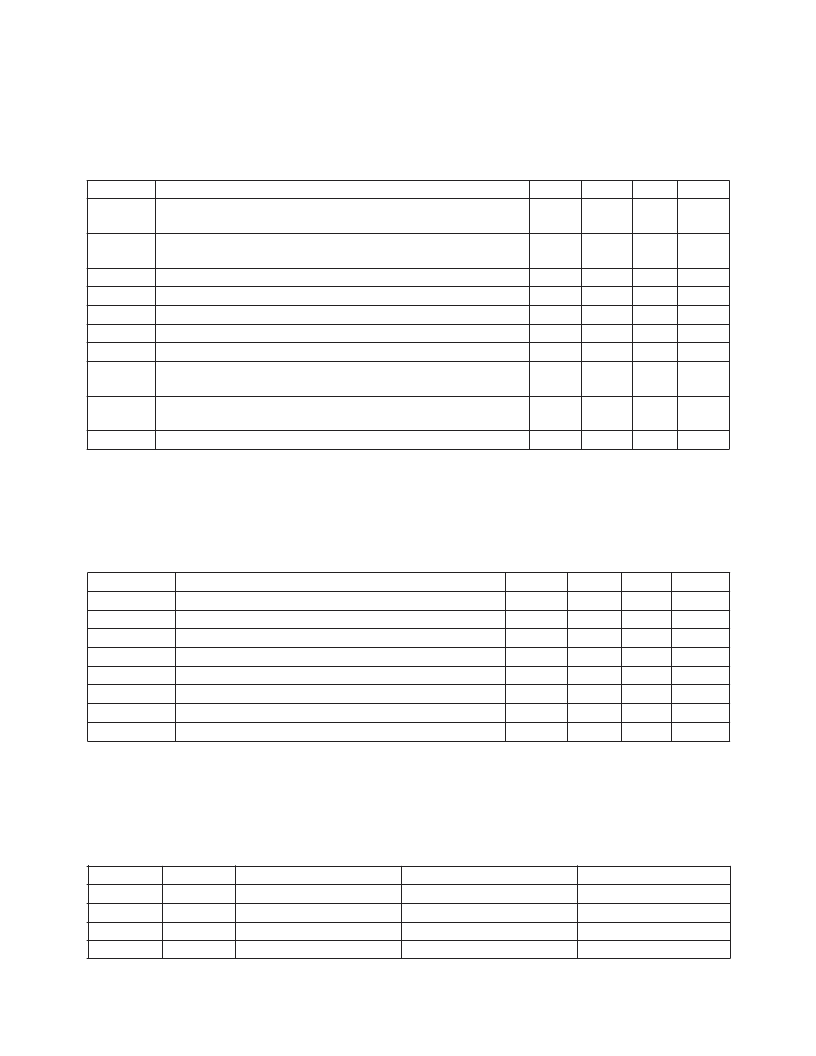

DC Electrical Specifications

Tc = 0

°

C to +85

°

C, V

CC

= 4.5 V to -5.5 V

Symbol

V

IH,TTL

TTL Input High Voltage Level, Guaranteed high signal for

all inputs

V

IL,TTL

TTL Input Low Voltage Level, Guaranteed low signal for all

inputs

V

OH,TTL

TTL Output High Voltage Level, I

OH

= -400

μ

A

V

OL,TTL

TTL Output Low Voltage Level, I

OL

= 1 mA

I

IH,TTL

Input High Current (Magnitude), V

IN

= V

CC

I

IL,TTL

Input Low Current (Magnitude), V

IN

= 0 Volts

V

IP,H50

H50 Input Peak-To-Peak Voltage

V

OP,BLL

BLL Output Peak-To-Peak Voltage, Terminated with 50

,

ac coupled

I

CC,Tx

Transmitter V

CC

Supply Current, with HCLKSEL off

Tc = 50

°

C

I

CC,Rx

Receiver V

CC

Supply Current, Tc = 50

°

C

Parameter

Units

V

Min.

2.0

Typ.

Max.

V

CC

V

0

0.8

V

V

μ

A

μ

A

mV

mV

2.4

0

V

CC

0.6

40

600

0.004

295

200

500

mA

385

470

mA

500

600

Note:

1. BLL outputs are measured with external 150

pull-up resistors to ground. Refer to Figure 23 for additional information.

HDMP-1022 (Tx), HDMP-1024 (Rx)

AC Electrical Specifications

Tc = 25

°

C

Symbol

t

r,TTLin

Input TTL Rise Time, 0.8 to 2.0 Volts

t

f,TTLin

Input TTL Fall Time, 2.0 to 0.8 Volts

t

r,TTLout

Output TTL Rise Time, 0.8 to 2.0 Volts, 10 pF load

t

f,TTLout

Output TTL Fall Time, 2.0 to 0.8 Volts, 10 pF load

t

r

,

BLL

BLL Rise Time, Terminated with 50

, ac coupled

t

f

,

BLL

BLL Fall Time, Terminated with 50

, ac coupled

VSWR

i,H50

H50 Input VSWR

VSWR

o,BLL

BLL Output VSWR

Note:

1. BLL outputs are measured with external 150

pull-up resistors to ground. Refer to Figure 23 for additional information.

Parameter

Units

nsec

nsec

nsec

nsec

psec

psec

Min.

Typ.

2

2

1.1

1.5

240

240

2:1

2:1

Max.

2.4

2.4

HDMP-1022 (Tx), HDMP-1024 (Rx)

Typical Lock-Up Time

Tc = 25

°

C

DIV1

DIV0

0

0

0

1

1

0

1

1

Note:

1. Measured in Local Loop-Back mode with the state machine engaged and 0 cable length.

HDMP-1022, msec

2.0

3.0

4.5

8.0

HDMP-1024, msec

2.2

3.2

4.7

11.0

LINK

[1]

, msec

2.5

3.5

5.0

12.0

相關PDF資料 |

PDF描述 |

|---|---|

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價格千兆位速率接收芯片) |

| HDMP-1032 | 1.4 GBd Transmitter Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 傳送器) |

| HDMP-1034 | 1.4 GBd Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate(帶CIMT編碼器/譯碼器和變量數(shù)據(jù)速率的1.4 GBd 接收器) |

| HDMP-1512 | Fibre Channel Transmitter Chipset(光纖通道傳送芯片) |

| HDMP-1514 | Fibre Channel Receiver Chipset(光纖通道接收芯片) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-1024 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Low Cost Gigabit Rate Transmit/Receive Chip Set with TTL I/Os |

| HDMP-1032 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1032A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:1.4 GBd Transmitter Chip with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:1.4 GBd Transmitter/Receiver Chip Set with CIMT Encoder/Decoder and Variable Data Rate |

| HDMP-1034A | 制造商:HP 制造商全稱:Agilent(Hewlett-Packard) 功能描述:Transmitter/Receiver Chip Set |

發(fā)布緊急采購,3分鐘左右您將得到回復。