- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄17021 > CDB5530U (Cirrus Logic Inc)BOARD EVAL FOR CS5530 PDF資料下載

參數(shù)資料

| 型號: | CDB5530U |

| 廠商: | Cirrus Logic Inc |

| 文件頁數(shù): | 20/36頁 |

| 文件大?。?/td> | 0K |

| 描述: | BOARD EVAL FOR CS5530 |

| 標準包裝: | 1 |

| ADC 的數(shù)量: | 1 |

| 位數(shù): | 24 |

| 采樣率(每秒): | 3.84k |

| 數(shù)據(jù)接口: | 串行 |

| 輸入范圍: | ±2.5 V |

| 在以下條件下的電源(標準): | 35mW @ 5V |

| 工作溫度: | -40°C ~ 85°C |

| 已用 IC / 零件: | CS5530 |

| 已供物品: | 板,CD |

| 相關(guān)產(chǎn)品: | CS5530-ISZR-ND - IC ADC 24BIT 1CH W/LNA 20-SSOP 598-1283-5-ND - IC ADC 24BIT 1CH W/LNA 20SSOP 598-1198-5-ND - IC DELTA-SIGMA 24BIT 1CH 20-SSOP |

| 其它名稱: | 598-1158 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

CS5530

DS742F3

27

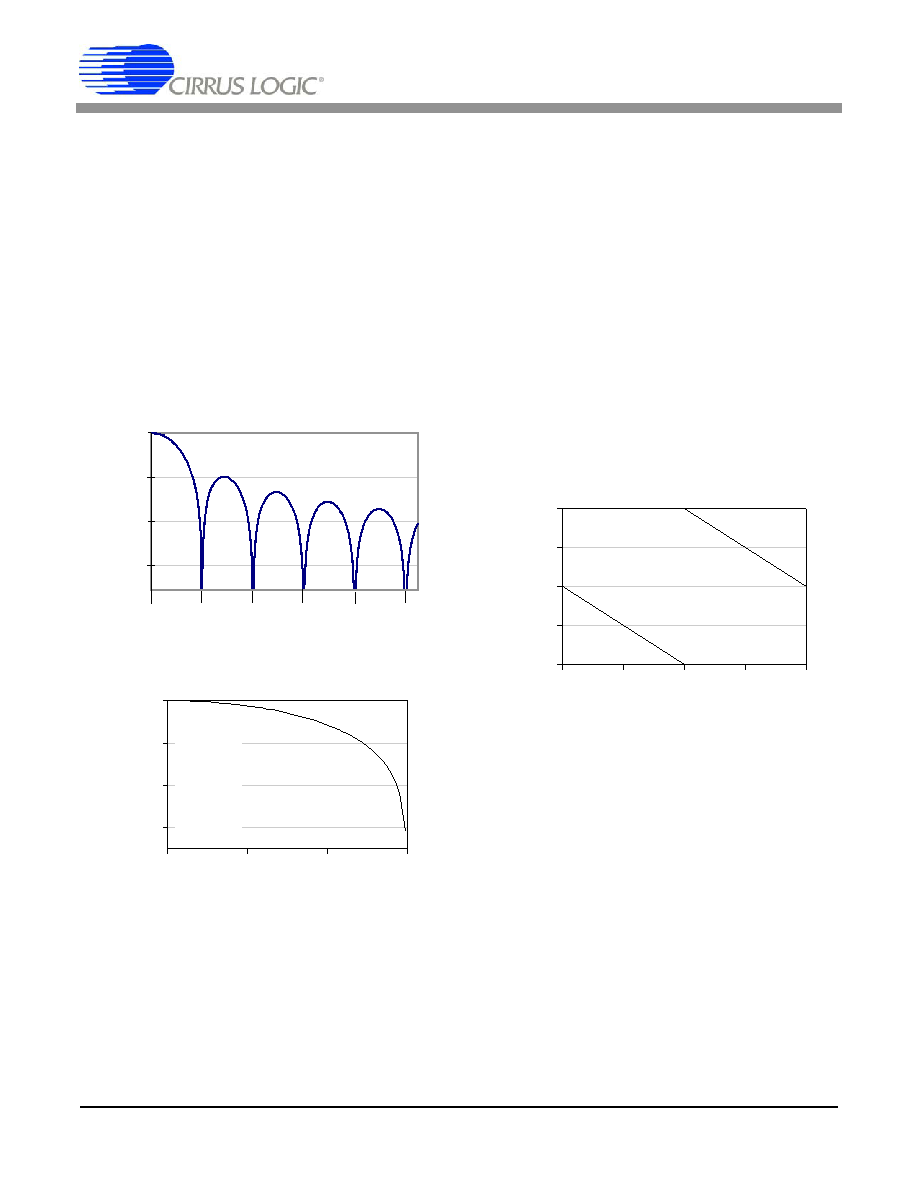

2.8 Digital Filter

The CS5530 has a linear phase digital filter which

is programmed to achieve a range of output word

rates (OWRs) as stated in the Configuration Regis-

ter Description section. The ADC uses a Sinc5 dig-

ital filter to output word rates at 3200 Sps and 3840

Sps (MCLK = 4.9152 MHz). Other output word

rates are achieved by using the Sinc5 filter followed

by a Sinc3 filter with a programmable decimation

rate.Figure 13 shows the magnitude response of the

magnitude and phase response of the filter at 120

Sps. The Sinc3 is active for all output word rates

except for the 3200 Sps and 3840 Sps (MCLK =

4.9152 MHz) rate. The Z-transforms of the two fil-

“D” is the programmable decimation ratio, which is

equal to 3840/OWR when FRS = 0 and 3200/OWR

when FRS = 1.

The converter’s digital filters scale with MCLK.

For example, with an output word rate of 120 Sps,

the filter’s corner frequency is at 31 Hz. If MCLK

is increased to 5.0 MHz, the OWR increases by

1.0175 percent and the filter’s corner frequency

moves to 31.54 Hz. Note that the converter is not

specified to run at MCLK clock frequencies greater

than 5 MHz.

Figure 13. Digital Filter Response (Word Rate = 60 Sps)

-120

-80

-40

0

Gain

(dB)

0

60

120

180

240

300

Frequency (Hz)

FRS = 0

-120

-80

-40

0

040

80

120

Frequency (Hz)

G

a

in

(

d

B

)

Flatness

Frequency

dB

2-0.01

4-0.05

6-0.11

8-0.19

10

-0.30

12

-0.43

14

-0.59

16

-0.77

19

-1.09

32

-3.13

Figure 14. 120 Sps Filter Magnitude Plot to 120 Hz

-180

-90

0

90

180

0

30

60

90

120

Frequency (Hz)

P

h

ase

(

D

eg

rees)

Figure 15. 120 Sps Filter Phase Plot to 120 Hz

Note:

See the text regarding the Sinc3 filter’s

decimation ratio “D”.

Sinc5

1

z 80

–

()5

1

z 16

–

()5

--------------------------

1

z 16

–

()3

1

z 4

–

()3

--------------------------

1

z 4

–

()2

1

z 2

–

()2

-----------------------

1

z 2

–

()3

1

z 1

–

()3

-----------------------

×

=

Sinc3

1

z D

–

()3

1

z 1

–

()3

-------------------------

=

Figure 16. Z-Transforms of Digital Filters

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SIP4613ADVP-T1-E3 | IC LOAD SW HISIDE 1A SC75-6 |

| CDB5534U | EVAL BOARD FOR CS5534 |

| AD9648-125EBZ | EVAL BOARD AD9648-125 |

| CDB5463U-Z | EVAL BOARD USB FOR CS5463 |

| AD9633-125EBZ | BOARD EVAL FOR AD9633 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CDB5532U | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開發(fā)工具 Eval Bd 24Bit ADC w/ Ultra Low-Noise USB RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| CDB5534U | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開發(fā)工具 Eval Bd 24Bit ADC w/ Ultra Low-Noise USB RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類型:ADC 工具用于評估:ADS130E08 接口類型:SPI 工作電源電壓:- 6 V to + 6 V |

| CDB5534U-Z | 功能描述:EVAL BD 24-BIT ADCS W/ULTRALN PG 制造商:cirrus logic inc. 系列:- 零件狀態(tài):在售 A/D 轉(zhuǎn)換器數(shù):1 位數(shù):24 采樣率(每秒):3.84k 數(shù)據(jù)接口:串行 輸入范圍:±2.5 V 不同條件下的功率(典型值):35mW @ 3.84kSPS 使用的 IC/零件:CS5534 所含物品:板,電纜 標準包裝:1 |

| CDB5540 | 制造商:Cirrus Logic 功能描述:EVAL BOARD FOR CS5540 - Bulk |

| CDB5541 | 制造商:Cirrus Logic 功能描述:EVAL BOARD FOR 5540 & 5541 N/A - Bulk 制造商:Cirrus Logic 功能描述:Tools Development kit For Use |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。