- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1974 > XCCACE-TQG144I (Xilinx Inc)IC ACE CONTROLLER CHIP TQ144 PDF資料下載

參數(shù)資料

| 型號(hào): | XCCACE-TQG144I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 3/69頁 |

| 文件大小: | 0K |

| 描述: | IC ACE CONTROLLER CHIP TQ144 |

| 產(chǎn)品變化通告: | XCCACE-TQG144I Discontinuation 31/Oct/2011 |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 控制器類型: | ACE 控制器 |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 30mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-TQFP(20x20) |

| 包裝: | 管件 |

| 其它名稱: | 122-1511-5 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

System ACE CompactFlash Solution

DS080 (v3.0) April 7, 2014

Product Specification

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Controlling the Number of Reserved Sectors

Windows 2000, Windows NT, and Windows 98 default to

one reserved sector when formatting. Therefore, formatting

the CF card using these Windows operating systems is not

problematical in this regard.

In Windows XP, however, the DOS format command auto-

matically formats the CF card with from two to eight

reserved sectors, depending on the density of the CF card.

Because the DOS format command does not allow specifi-

cation of the number of reserved sectors, an alternate disk

formatting

utility

(such

as

mkdosfs,

available

from

http://www1.mager.org/mkdosfs) must be used. When

the CF card is correctly formatted, Windows XP can be

used to perform normal file access (read/write) operations

without causing any additional problems.

Microprocessor Interface (MPU)

The MPU Interface provides a useful means of monitoring

the status of and controlling the System ACE CF controller,

as well as CompactFlash card READ / WRITE data. The

MPU is not required for normal operation, but when used, it

provides numerous capabilities. This interface enables

communication between an MPU device and a Compact-

Flash module and the FPGA target system.

The MPU interface is composed of a set of registers that

provide a means for communicating with CompactFlash

control

logic,

configuration

control

logic,

and

other

resources in the System ACE CF controller. Specifically, this

interface can be used to read the identity of a Compact-

Flash device and read/write sectors from or to a Compact-

Flash device.

The MPU interface can also be used to control configuration

flow. The MPU interface enables monitoring of System ACE

CF controller configuration status and error conditions. The

MPU interface can be used to delay configuration, start con-

figuration, determine the source of configuration (Compact-

Flash or MPU), control the bitstream version, reset the

device, etc.

Two important issues should be understood when using the

microprocessor port:

For the System ACE CF controller to be properly

synchronized, the device driving the MPU interface

must be synchronized to the CLK signal

The MPU must comply with System ACE timing

requirements

This general-purpose microprocessor interface can update

the CompactFlash, read the ACE status, or obtain direct

access to the JTAG configuration ports using the ACE

Microprocessor commands. This interface supports either

8-bit (default) or 16-bit data transfers. The bus width can be

configured dynamically.

All communications between the System ACE CF controller

and a host microprocessor involve transfer of data to or from

ACE registers. There are 128 addressable registers in 8-bit

mode and 64 addressable registers in 16-bit mode. For

easy selection of a new configuration from CompactFlash

data, the MPU interface allows for easy reconfiguration of

an FPGA chain or capability.

When using the MPU interface as the configuration source,

the CFGTCK output for the System ACE CF controller

device is derived from the CLK input to the System ACE CF

controller (supplied by the MPU), and the operating fre-

quency of the CFGTCK is the same as CLK.

The minimum clock operating frequency is 0 MHz.

The maximum clock operating frequency is either 33

MHz or the maximum JTAG TCK clock speed dictated

by the devices in the JTAG chain and/or the board

design. The lowest of these values should be used.

The following sections describe supported operations when

using the MPU interface.

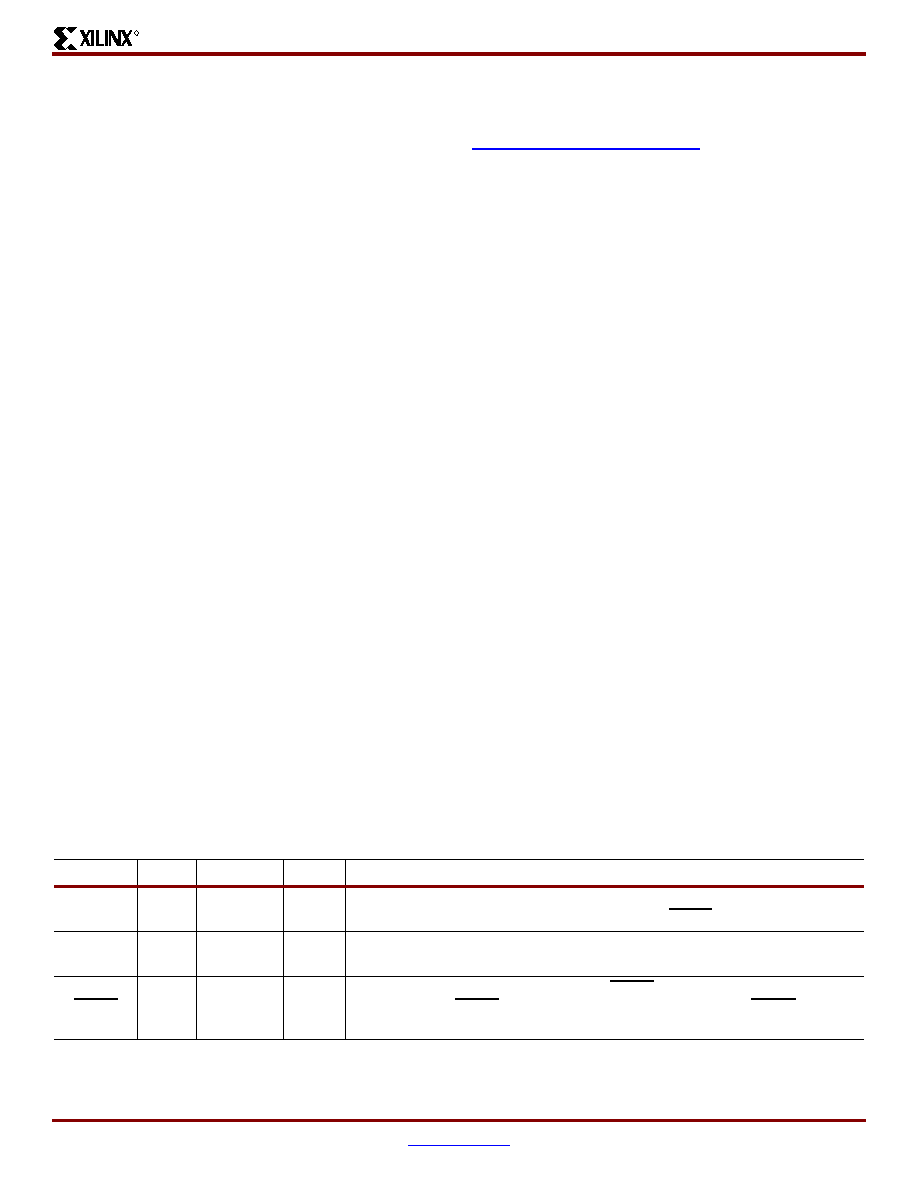

MPU Port Signal Description

MPU interface port signals are described in Table 6.

Table 6: MPU Interface Port Signal Description

Name

Width

Direction

Active

Description

MPA

7

In

N/A

Synchronous address inputs. The internal address register is loaded by MPA

by a combination of the rising edge of CLK and MPCE LOW.

MPD

16

In/Out

N/A

Synchronous data input/output pins. Both the data input and output path are

registered and triggered by the rising edge of CLK.

MPCE

1In

LOW

Synchronous active LOW chip enable. MPCE LOW is used to enable the

MPU interface. MPCE LOW is also used in conjunction with MPOE LOW to

enable the MPD output.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCF128XFTG64C | IC PROM SRL 128M GATE 64-FTBGA |

| XCF32PFS48C | IC PROM SRL 1.8V 32M 48CSBGA |

| XCR3256XL-7CS280C | IC CPLD 256MCELL 3.3V HP 280CSP |

| XCS10-3VQG100C | IC FPGA 5V C-TEMP 100-VQFP |

| XCV600E-8HQ240C | IC FPGA 1.8V C-TEMP 240-HQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCCAE7C13N | 制造商:Schneider Electric 功能描述:ABSOLUTE ENCDER SINGLE TURN 13 BITS 11 30V DC 制造商:SCHNEIDER ELECTRIC 功能描述:ABSOLUTE ENCDER SINGLE TURN |

| XCC-C0 | 制造商:Excelsys Technologies 功能描述:ELECTRONIC PART |

| XCCN0000 | 制造商:Red Lion Controls 功能描述:OPTION CARD, DSP/MC CANOPEN OPTION CARD 制造商:Red Lion Controls 功能描述:DSP/MC CANOPEN OPTION CARD |

| XCCPM23121L10 | 制造商:Schneider Electric 功能描述:pre-wired M23 female connector - for incremental encoder - cable 10m 制造商:Schneider Electric 功能描述:Cable Assembly Pre-Wired Pigtail 10m 10 POS M23 Circular F |

| XCCPM23121L2 | 制造商:Schneider Electric 功能描述:PRE WIRED CONNECTOR M23 10 WIRES INCREM 2M 制造商:SCHNEIDER ELECTRIC 功能描述:Cable Assembly 2m 10 POS M23 Circular |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。