- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384021 > TMS320F28335_1 (Texas Instruments, Inc.) Variable Capacitance Diode for TV Tuner VHF Tuning; Ratings VR (V): 32; Characteristics n: 12.0 min; Characteristics rs (ohm) max: 0.85; Characteristics C (pF) max: C2 = 32.2 to 37.5 C25 = 2.57 to 3.0; Characteristics CVR/CVR: 2/25; Cl: 2.777; Package: UFP PDF資料下載

參數(shù)資料

| 型號: | TMS320F28335_1 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Variable Capacitance Diode for TV Tuner VHF Tuning; Ratings VR (V): 32; Characteristics n: 12.0 min; Characteristics rs (ohm) max: 0.85; Characteristics C (pF) max: C2 = 32.2 to 37.5 C25 = 2.57 to 3.0; Characteristics CVR/CVR: 2/25; Cl: 2.777; Package: UFP |

| 中文描述: | 數(shù)字信號控制器(DSC) |

| 文件頁數(shù): | 148/166頁 |

| 文件大小: | 1889K |

| 代理商: | TMS320F28335_1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁當(dāng)前第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

www.ti.com

A

XCLKOUT

(/1 Mode)

XHOLD

XZCS0, XZCS6, XZCS7

XD[31:0], XD[15:0]

Valid

XHOLDA

t

d(HL-Hiz)

t

d(HH-HAH)

High-Impedance

XA[19:0]

Valid

Valid

High-Impedance

t

d(HH-BV)

t

d(HL-HAL)

(A)

(B)

XR/W

TMS320F28335, TMS320F28334, TMS320F28332

Digital Signal Controllers (DSCs)

SPRS439B–JUNE 2007–REVISED OCTOBER 2007

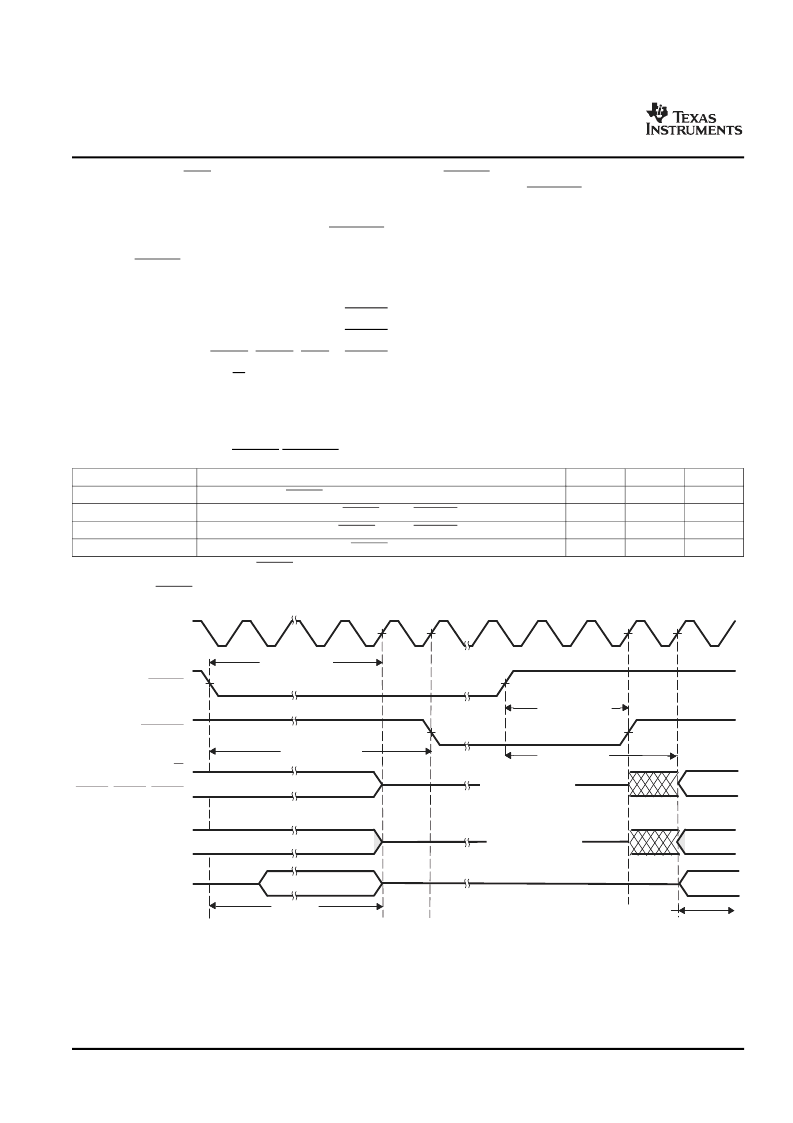

On a reset (XRS), the HOLD mode bit is set to 0. If the XHOLD signal is active low on a system reset, the

bus and all signal strobes must be in high-impedance mode, and the XHOLDA signal is also driven active

low.

When HOLD mode is enabled and XHOLDA is active low (external bus grant active), the CPU can still

execute code from internal memory. If an access is made to the external interface, the CPU is stalled until

the XHOLD signal is removed.

An external DMA request, when granted, places the following signals in a high-impedance mode:

XA[19:0]

XD[31:0], XD[15:0]

XWE0, XWE1, XRD

XR/W

XZCS0

XZCS6

XZCS7

All other signals not listed in this group remain in their default or functional operational modes during these

signal events.

Table 6-49. XHOLD/XHOLDA Timing Requirements (XCLKOUT = XTIMCLK)

(1)(2)

MIN

MAX

4t

c(XTIM)

5t

c(XTIM)

3t

c(XTIM)

4t

c(XTIM)

UNIT

ns

ns

ns

ns

t

d(HL-HiZ)

t

d(HL-HAL)

t

d(HH-HAH)

t

d(HH-BV)

Delay time, XHOLD low to Hi-Z on all address, data, and control

Delay time, XHOLD low to XHOLDA low

Delay time, XHOLD high to XHOLDA high

Delay time, XHOLD high to bus valid

(1)

When a low signal is detected on XHOLD, all pending XINTF accesses will be completed before the bus is placed in a high-impedance

state.

The state of XHOLD is latched on the rising edge of XTIMCLK.

(2)

A.

B.

All pending XINTF accesses are completed.

Normal XINTF operation resumes.

Figure 6-29. External Interface Hold Waveform

148

Electrical Specifications

Submit Documentation Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS4024 | 9 X 64 DIGITAL STORAGE BUFFER (FIFO) |

| TMS4024JC | 9 X 64 DIGITAL STORAGE BUFFER (FIFO) |

| TMS4024NC | 9 X 64 DIGITAL STORAGE BUFFER (FIFO) |

| TMS4256-15SDE | 262,144-BIT DYNAMIC RANDOM-ACCESS MEMORIES |

| TMS4257-15SDE | 262,144-BIT DYNAMIC RANDOM-ACCESS MEMORIES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320F28335PGFA | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Digital Signal Controller RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F28335PGFA | 制造商:Texas Instruments 功能描述:IC DSC 32BIT 512KB 150MHZ 1.995V LQFP176 |

| TMS320F28335PTPQ | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Delfino Micrcntrlr RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F28335PTPS | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Delfino Micrcntrlr RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F28335ZHHA | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Digital Signal Controller RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。