- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385819 > SC28L92 (NXP Semiconductors N.V.) 3.3V- 5.0V Dual universal asynchronous receiver/transmitter (DUART)(3.3V- 5.0V雙通用異步接收器/傳送器) PDF資料下載

參數(shù)資料

| 型號: | SC28L92 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 3.3V- 5.0V Dual universal asynchronous receiver/transmitter (DUART)(3.3V- 5.0V雙通用異步接收器/傳送器) |

| 中文描述: | 3.3 - 5.0V雙路通用異步接收/發(fā)送器(杜阿爾特)(3.3 - 5.0V雙通用異步接收器/傳送器) |

| 文件頁數(shù): | 23/44頁 |

| 文件大小: | 284K |

| 代理商: | SC28L92 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

Philips Semiconductors

Product specification

SC28L92

3.3V–5.0V Dual Universal Asynchronous

Receiver/Transmitter (DUART)

2000 Jan 21

23

For the receiver these bits control the number of FIFO positions

filled when the receiver will attempt to interrupt. After the reset the

receiver FIFO is empty. The default setting of these bits cause the

receiver to attempt to interrupt when it has one or more bytes in it.

MR0[5:4]

—Tx interrupt fill level.

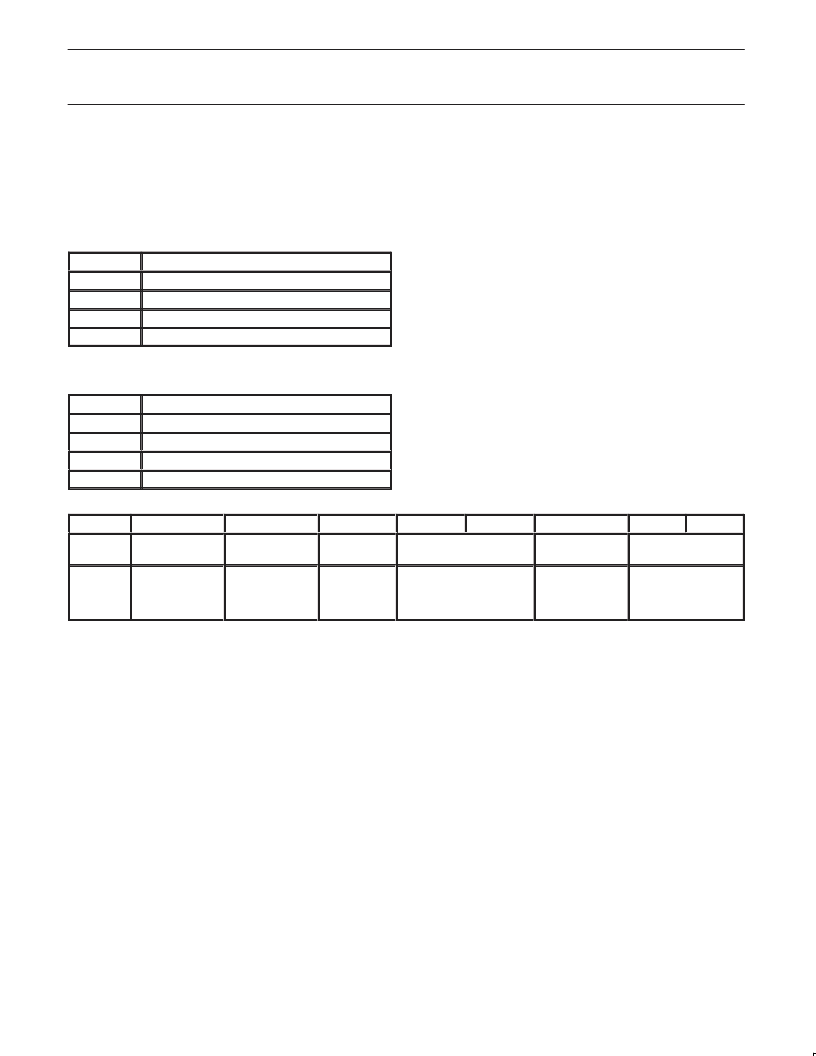

Table 4. Transmitter FIFO interrupt fill level

MR0(3) = 0 (8 bytes)

ááááááááááááááááá

ááááááááááááááááá

ááááááááááááááááá

ááááááááááááááááá

ááááááááááááááááá

00

01

11

8 bytes empty (Tx EMPTY)

4 or more bytes empty

1 or more bytes empty (Tx RDY)

10

6 or more bytes empty

Table 4a. Transmitter FIFO interrupt fill

level MR0(3) = 1 (16 bytes)

ááááááááááááááááá

ááááááááááááááááá

ááááááááááááááááá

ááááááááááááááááá

ááááááááááááááááá

MR1A

Mode Register 1

00

01

11

16 bytes empty (Tx EMPTY)

8 or more bytes empty

1 or more bytes empty (Tx RDY)

10

12 or more bytes empty

For the transmitter these bits control the number of FIFO positions

empty when the transmitter will attempt to interrupt. After the reset

the transmit FIFO has 8 bytes empty. It will then attempt to interrupt

as soon as the transmitter is enabled. The default setting of the MR0

bits (5:4) condition the transmitter to attempt to interrupt only when it

is completely empty. As soon as one byte is loaded, it is no longer

empty and hence will withdraw its interrupt request.

MR0[3]

—Selects the FIFO depth at 8 or 16 bytes. See Tables 3 and 4

MR0[2:0]

—These bits are used to select one of the six baud rate

groups.

See Table 5 for the group organization.

000 Normal mode

001 Extended mode I

100 Extended mode II

Other combinations of MR2[2:0] should not be used

Note

: MR0[3:0] are not used in channel B and should be set to 0.

áááááááááááááááááááááááááááááá

áááááááááááááááááááááááááááááá

á

á

áááááááááááááááááááááááááááááá

NOTE:

In block error mode, block error conditions must be cleared by using the error reset command (command 4x) or a receiver reset.

Addr

á

BIT 7

á

BIT 6

BIT 5

BIT 4

BIT 3

á

BIT 2

á

BIT 1

BIT 0

áááááááááááááááááááááááááááááá

MR1A/

Rx CONTROLS

RxINT

ERROR

ááá

ááá

11 = Multi-drop Mode

PARITY MODE

ááá

ááá

PARITY TYPE

ááááá

ááááá

11 = 8

BITS PER

áá

á

0x08

ááá

ááá

á

1 = Yes

áááá

áááá

á

á

1 = FFULL

á

á

1 = Block

áááááá

áááááá

á

01 = Force Parity

á

1 = Odd

á

á

01 = 6

MR1A is accessed when the Channel A MR pointer points to MR1.

The pointer is set to MR1 by RESET or by a ‘set pointer’ command

applied via CR command 1. After reading or writing MR1A, the

pointer will point to MR2A.

MR1A[7]—Channel A Receiver Request-to-Send Control

(Flow Control)

This bit controls the deactivation of the RTSAN output (OP0) by the

receiver. This output is normally asserted by setting OPR[0] and

negated by resetting OPR[0]. Proper automatic operation of flow

control requires OPR[0] (channel A) or OPR[1] (channel B) to be set

to logical 1.

MR1A[7] = 1 causes RTSAN to be negated (OP0 is driven to a ‘1’

[V

CC

]) upon receipt of a valid start bit if the Channel A FIFO is full.

This is the beginning of the reception of the ninth byte. If the FIFO is

not read before the start of the tenth or 17th byte, an overrun

condition will occur and the tenth or 17th or 17th byte will be lost.

However, the bit in OPR[0] is not reset and RTSAN will be asserted

again when an empty FIFO position is available. This feature can be

used for flow control to prevent overrun in the receiver by using the

RTSAN output signal to control the CTSN input of the transmitting

device.

MR1[6]

—Bit 1 of the receiver interrupt control. See description

under MR0[6].

MR1A[5]—Channel A Error Mode Select

This bit select the operating mode of the three FIFOed status bits

(FE, PE, received break) for Channel A. In the ‘character’ mode,

status is provided on a character-by-character basis; the status

applies only to the character at the top of the FIFO. In the ‘block’

mode, the status provided in the SR for these bits is the

accumulation (logical-OR) of the status for all characters coming to

the top of the FIFO since the last ‘reset error’ command for

Channel A was issued.

MR1A[4:3|—Channel A Parity Mode Select

If ‘with parity’ or ‘force parity’ is selected a parity bit is added to the

transmitted character and the receiver performs a parity check on

incoming data MR1A[4:3] = 11 selects Channel A to operate in the

special multi-drop mode described in the Operation section.

MR1A[2]—Channel A Parity Type Select

This bit selects the parity type (odd or even) if the ‘with parity’ mode

is programmed by MR1A[4:3], and the polarity of the forced parity bit

if the ‘force parity’ mode is programmed. It has no effect if the ‘no

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC3011B-1 | 600.0 MHz Differential Sine-Wave Clock |

| SC3015B | 550.0 MHz Differential Sine-Wave Clock |

| SC3017B | 400.0 MHz Differential Sine-Wave Clock |

| sc3018b | Quartz SAW Frequency Stability |

| SC3019B | 500.0 MHz Differential Sine-Wave Clock |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC28L92A1A | 制造商:NXP Semiconductors 功能描述:UART DUAL 3.3V OR 5V SMD 28L92 |

| SC28L92A1A,512 | 功能描述:UART 接口集成電路 3V-5V 2CH UART INTEL/MOT INTRF RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L92A1A,518 | 功能描述:UART 接口集成電路 3V-5V 2CH UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L92A1A,529 | 功能描述:UART 接口集成電路 3V-5V 2CH UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC28L92A1A512 | 制造商:NXP Semiconductors 功能描述:IC DUAL UART FIFO 1MBPS 5.5V LCC-44 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。