- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372115 > SAA7390 (NXP Semiconductors N.V.) High performance Compact Disc-Recordable CD-R controller PDF資料下載

參數(shù)資料

| 型號: | SAA7390 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | High performance Compact Disc-Recordable CD-R controller |

| 中文描述: | 高性能式光盤CD - R光盤控制器 |

| 文件頁數(shù): | 32/76頁 |

| 文件大?。?/td> | 366K |

| 代理商: | SAA7390 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

1996 Jul 02

32

Philips Semiconductors

Preliminary specification

High performance Compact

Disc-Recordable (CD-R) controller

SAA7390

10.2

Front-end status and control

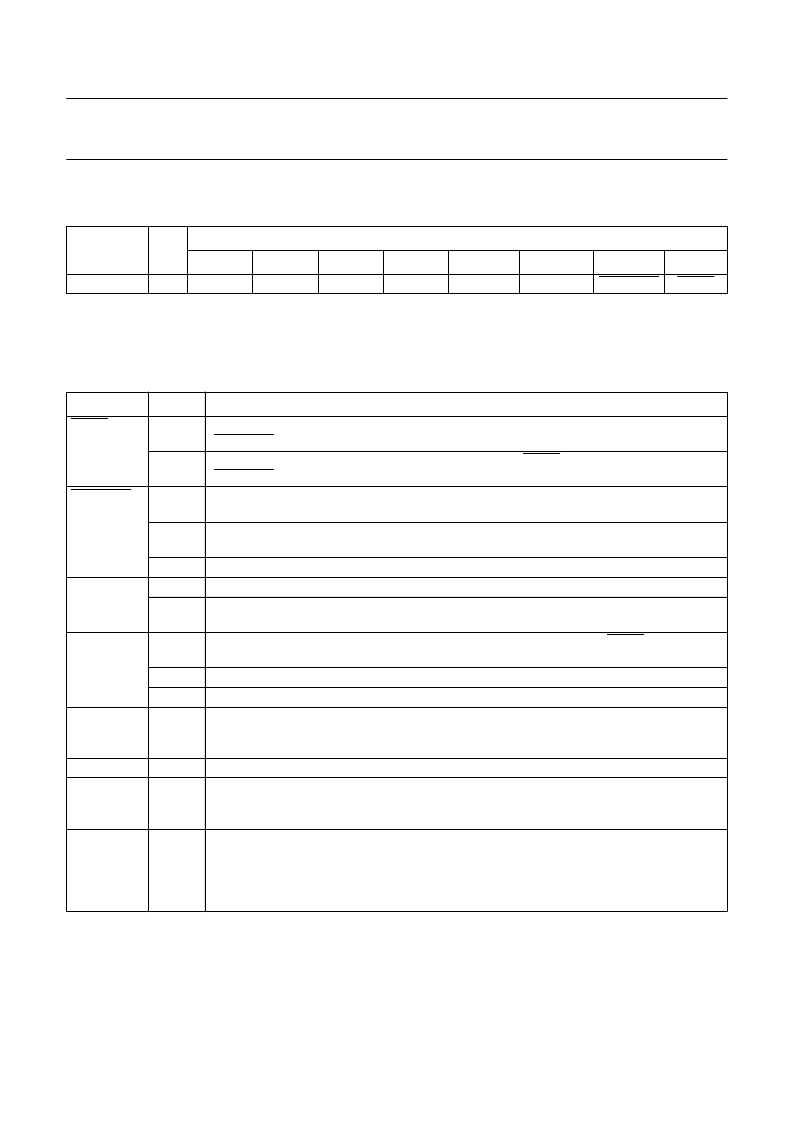

Table 39

Front-end control: 0xF0BB; note 1

Note

1.

Register 0xF0BB controls the front-end of the SAA7390. The naming convention used here is similar to that used in

the block decoders.

Table 40

FECTL field descriptions

MNEMONIC

R/W

DATA BYTE

7

6

5

4

3

2

1

0

FECTL

R/W

SIM_EOF

RSMD

BREAK

RWMD

ENABRED AUDMODE SYNASYN

ECMD

FIELD

LOGIC

DESCRIPTION

ECMD

0

Data is shifted in and stored when the next synchronization pattern is detected;

(SYNASYN = 1 and AUDMODE = 0).

Data flow stop just before next synchronization pattern. ECMD is set on a reset condition;

(SYNASYN = 1).

Synchronous/asynchronous selection; this controls the method by which data is started and

stopped by the block decoder, only operates in data mode.

Causes a ‘panic stop’. A partial frame will reside in current and subsequent buffers unless

SIM_EOF is set then cleared; (ECMD = 1).

Data is started and stopped on frame boundaries (on synchronization patterns).

Data mode. Cleared on reset.

Audio mode, where the bit clock is shifted to accommodate EIAJ format. HQRDY in

INTRFLG follows HDRRDY in data mode and QFRMDRY in audio mode.

Enable red book to data path; while in audio mode, this is equivalent to ECMD in the data

mode. No asynchronous stop is provided in the audio mode.

Data flow will stop when the next F1 C-flag is detected. Cleared on a reset condition.

Red book data is input to buffer after the detection of the next F1 C-flag.

This must be pulsed HIGH then LOW every 212 ms to prevent the watch-dog timer from

resetting the SAA7390 and the drive. The length of the reset pulse is 967

μ

s. If RWMD is set,

the watch-dog timer is disabled.

When set, the S2B UART transmitter output is held HIGH.

When the pulse is HIGH then LOW, the block decoder begins to search for a synchronization

pattern in the data bitstream. Once a synchronization pattern is found, MODE, MINS, SECS,

and FRMS become valid.

This provides a firmware reset to the frame sequencer and parts of the buffer manager.

This would be required if an asynchronous stop of the data stream occurs. Pulsing this HIGH

then LOW resets all counters and establishes a ‘beginning of frame’ state. DCOACT in

RDDSTAT must be LOW to allow SIM_EOF to have any effect. If SIM_EOF is set, no data or

sub-code is stored in the buffer.

1

SYNASYN

0

1

0

1

AUDMODE

ENABRED

0

1

RWMD

BREAK

RSMD

SIM_EOF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7390GP | High performance Compact Disc-Recordable CD-R controller |

| SAA7501WP | ARD/ZDF NR.3R1 DIGITAL DECODER|LDCC|68PIN|PLASTIC |

| SAA7707H | Shaft; Style: 1 - light; Applicable Model: LE-P / LEL-W |

| SAA7710T | High Quality Audio-Performance Digital Add-On Processor For Digital Sound Systems.(應(yīng)用在數(shù)字聲音系統(tǒng)的高品質(zhì)音頻性能數(shù)字附加處理器) |

| SAA7715AH | Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7390GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High performance Compact Disc-Recordable CD-R controller |

| SAA7391 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7391H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7392 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Channel encoder/decoder CDR60 |

| SAA7392HL | 制造商:NXP Semiconductors 功能描述:CD-ROM INTERFACE, 80 Pin, Plastic, QFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。