- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372115 > SAA7390 (NXP Semiconductors N.V.) High performance Compact Disc-Recordable CD-R controller PDF資料下載

參數(shù)資料

| 型號(hào): | SAA7390 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | High performance Compact Disc-Recordable CD-R controller |

| 中文描述: | 高性能式光盤CD - R光盤控制器 |

| 文件頁數(shù): | 29/76頁 |

| 文件大?。?/td> | 366K |

| 代理商: | SAA7390 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

1996 Jul 02

29

Philips Semiconductors

Preliminary specification

High performance Compact

Disc-Recordable (CD-R) controller

SAA7390

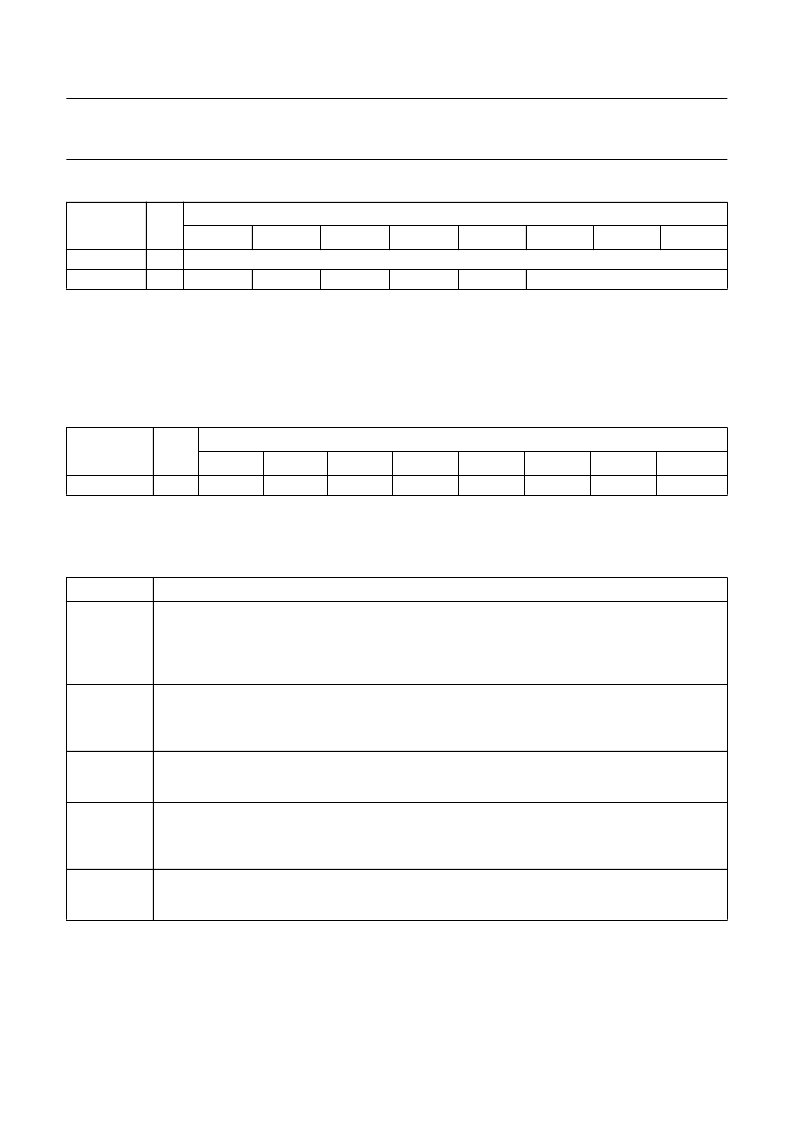

Table 31

Track descriptor block address: 0xF096 and 0xF097; note 1

Note

1.

Registers 0xF096 and 0xF097 contain the frame address of the TDB. When the buffer manager frame count equals

the contents of this register and the TDB_EN bit is set in BMFECTL, the frame counter will not be allowed to

increment until TDB_CNT equals zero.

9.4

Miscellaneous control registers

Table 32

Host interface direction and audio mode control: 0xF0C1; note 1

Note

1.

Register 0xF0C1 controls the data path to the host interface and some audio functions.

Table 33

WTDIR field descriptions

MNEMONIC

R/W

DATA BYTE

7

6

5

4

3

2

1

0

TDB

TDB

R/W

R/W

TDB address 7 to TDB address 0

TDB address 10 to 8

MNEMONIC

R/W

DATA BYTE

7

6

5

4

3

2

1

0

WTDIR

R/W

CBSB

OVER4X

BSB

HOSTDIR AUTOSTR

FIELD

DESCRIPTION

AUTOSTR

Automatic store; default is off. When set HIGH, the front-end will automatically begin storing data or

audio when the contents of the header/Q-channel registers equals the contents of the STRTMIN,

STRTSEC and STRTFRM registers. If a header/Q-channel error occurs to invalidate the address,

auto-store is inhibited. Storing of data will continue until the contents of the STOPCNT equals zero, at

which time it will automatically stop.

Host direction; default LOW. This selects the microcontroller data path to the SCSI interface. Setting

this HIGH selects the buffer managers DMA path. When using a 53CF92A, this should be set and left

HIGH since the microcontroller has a separate command path into the 53CF92A whereas the

53CF90B requires the buffer manager and microcontroller to share the same path.

Byte swap bit. Defaults to swapping the most significant byte and least significant byte in the audio

mode such that the least significant byte of all audio samples is stored at even addresses in the

DRAM. Setting this HIGH causes the audio data to be stored in the same way as in the data mode.

4

×

over-sampling bit selection; default LOW select transmit, or no over-sampling, mode for the

sub-code and C-flag UARTs. Setting this bit HIGH will cause the sub-code and C-flag data to be

sampled at one quarter the data rate allowing Q-channel information to be correctly stored in the

registers while the CD-60 is outputting audio data at 4

×

over-sampling.

CBD2 byte swap bit; default LOW allows data from the DRAM buffer to be sent to the CDB2 normally

(data mode). When set HIGH, the high byte and low byte are swapped since data from the host will be

swapped. As a result, Red book in the bypass mode will be correctly aligned.

HOSTDIR

BSB

OVER4X

CBSB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7390GP | High performance Compact Disc-Recordable CD-R controller |

| SAA7501WP | ARD/ZDF NR.3R1 DIGITAL DECODER|LDCC|68PIN|PLASTIC |

| SAA7707H | Shaft; Style: 1 - light; Applicable Model: LE-P / LEL-W |

| SAA7710T | High Quality Audio-Performance Digital Add-On Processor For Digital Sound Systems.(應(yīng)用在數(shù)字聲音系統(tǒng)的高品質(zhì)音頻性能數(shù)字附加處理器) |

| SAA7715AH | Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7390GP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:High performance Compact Disc-Recordable CD-R controller |

| SAA7391 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7391H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:ATAPI CD-R block encoder/decoder |

| SAA7392 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Channel encoder/decoder CDR60 |

| SAA7392HL | 制造商:NXP Semiconductors 功能描述:CD-ROM INTERFACE, 80 Pin, Plastic, QFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。