- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382386 > PDC2 Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號: | PDC2 |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項(xiàng)-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 5/25頁 |

| 文件大小: | 291K |

| 代理商: | PDC2 |

5

Peripheral Data Controller 2 (PDC2)

1734B

–

CASIC

–

02/02

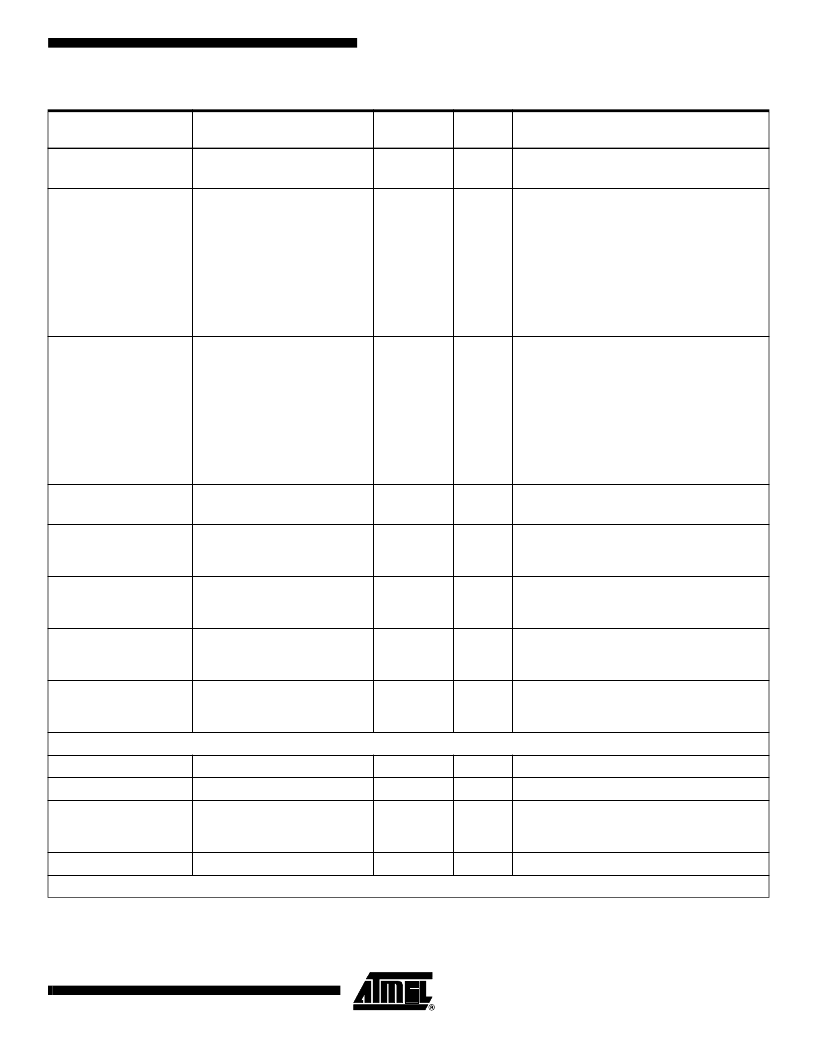

periph_tx_rdy

[(per_n-1):0]

Peripheral Transmitter Ready

Input

High

Once the holding transmit register is

available, one of these bits is set to 1

periph_rx_size

[(2*per_n)-1:0]

Peripheral Transfer Sizes for

Reception Side

Input

–

The per_n is the number of peripherals

connected to the PDC2. This value changes

the memory pointer. Two bits are reserved for

each peripheral, for example, with two

USARTs and one SPI, the size of transfer on

the receiver side for:

USART0 = periph_rx_size[1:0],

USART1 = periph_rx_size[3:2] and

SPI0 = periph_rx_size[5:4]

periph_tx_size

[(2*per_n)-1:0]

Peripheral Transfer Sizes for

Transmission Side

Input

–

The per_n is the number of peripherals

connected to the PDC2. This value changes

the memory pointer. Two bits are reserved for

each peripheral, for example, with two

USARTs and one SPI, the size of transfer on

the transmit side for:

USART0 = periph_tx_size[1:0],

USART1 = periph_tx_size[3:2] and

SPI0 = periph_tx_size[5:4]

periph_select

[(per_n-1):0]

Peripheral selects

Input

High

From host (Bridge)

–

also input of each

peripheral connected

periph_rx_end

[(per_n-1):0]

Peripheral receive end

Output

High

End of receive transfer (each bit corresponds

to a peripheral)

–

the associated buffer for the

channel is full

periph_tx_end

[(per_n-1):0]

Peripheral Transmit End

Output

High

End of transmit transfer (each bit

corresponds to a peripheral)

–

the associated

buffer for the channel is empty

rx_buffer_full

[(per_n-1):0]

Peripheral Receive Buffer Full

Output

High

End of receive transfer (each bit corresponds

to a peripheral)

–

the associated buffers for

the channel are full

tx_buffer_empty

[(per_n-1):0]

Peripheral Transmit Buffer

Empty

Output

High

End of transmit transfer (each bit

corresponds to a peripheral)

–

the associated

buffers for the channel are empty

Bridge Interface

pdc_add[20:0]

PDC2 Address Bus

Output

–

Used by the Bridge to access the peripherals

pdc_sel

PDC2 Select

Output

High

Used by the Bridge to access the peripherals

pdc_size[1:0]

PDC2 Size of Transfer

Output

–

Multiplex the spi_size inputs

–

used by the

Bridge to determine the size of the transfer

between memories and the SPI

pdc_write

PDC2 Write

Output

High

Used by the Bridge to access the peripherals

Memory Management Unit/EBI

Table 1.

PDC2 Pin Description (Continued)

Name

Definition

Type

Active

Level

Comments

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1284P11 | 3.3V Parallel interface transceiver/buffer |

| PDI1394P11A | 3-port physical layer interface |

| PDI1394P11ABD | 3-port physical layer interface |

| PDI1394P25BY | 1-port 400 Mbps physical layer interface |

| PDI20AC1H0R | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDC-20-1 | 制造商:MINI 制造商全稱:Mini-Circuits 功能描述:6 to 30 dB COUPLING up to 10W 5 kHz to 2000 MHz |

| PDC-20-1W | 制造商:MINI 制造商全稱:Mini-Circuits 功能描述:6 to 30 dB COUPLING up to 10W 5 kHz to 2000 MHz |

| PDC20275 | 制造商:PROMISE 功能描述: 制造商:Promise Tech 功能描述: |

| PDC20275-E3 | 制造商:Promise Tech 功能描述: |

| PDC-20-3 | 制造商:MINI 制造商全稱:Mini-Circuits 功能描述:6 to 30 dB COUPLING up to 10W 5 kHz to 2000 MHz |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。