- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382377 > PCA5010 (NXP Semiconductors N.V.) Pager baseband controller PDF資料下載

參數(shù)資料

| 型號(hào): | PCA5010 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Pager baseband controller |

| 中文描述: | 傳呼機(jī)基帶控制器 |

| 文件頁(yè)數(shù): | 86/112頁(yè) |

| 文件大小: | 627K |

| 代理商: | PCA5010 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)當(dāng)前第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)

1998 Nov 02

86

Philips Semiconductors

Product specification

Pager baseband controller

PCA5010

Notes

1.

DC/DC converter configured with inductor of L = 470

μ

H, SRL = 5

, input capacitance of C

i

= 4.7

μ

F, ESR = 0.5

,

V

DD

output capacitor C

o

= 4.7

μ

F, ESR = 0.5

, R

BAT

< 1

.

This parameter is not tested during production; it is guaranteed by design.

This parameter depends on external components.

At high load or low battery voltage the inductor charge time can be extended to a full XTL1 period, while the minimum

inductor discharge time is a half XTL1 period.

The execution time is strongly dependant on command type and addressing mode (see also Table 60).

2.

3.

4.

5.

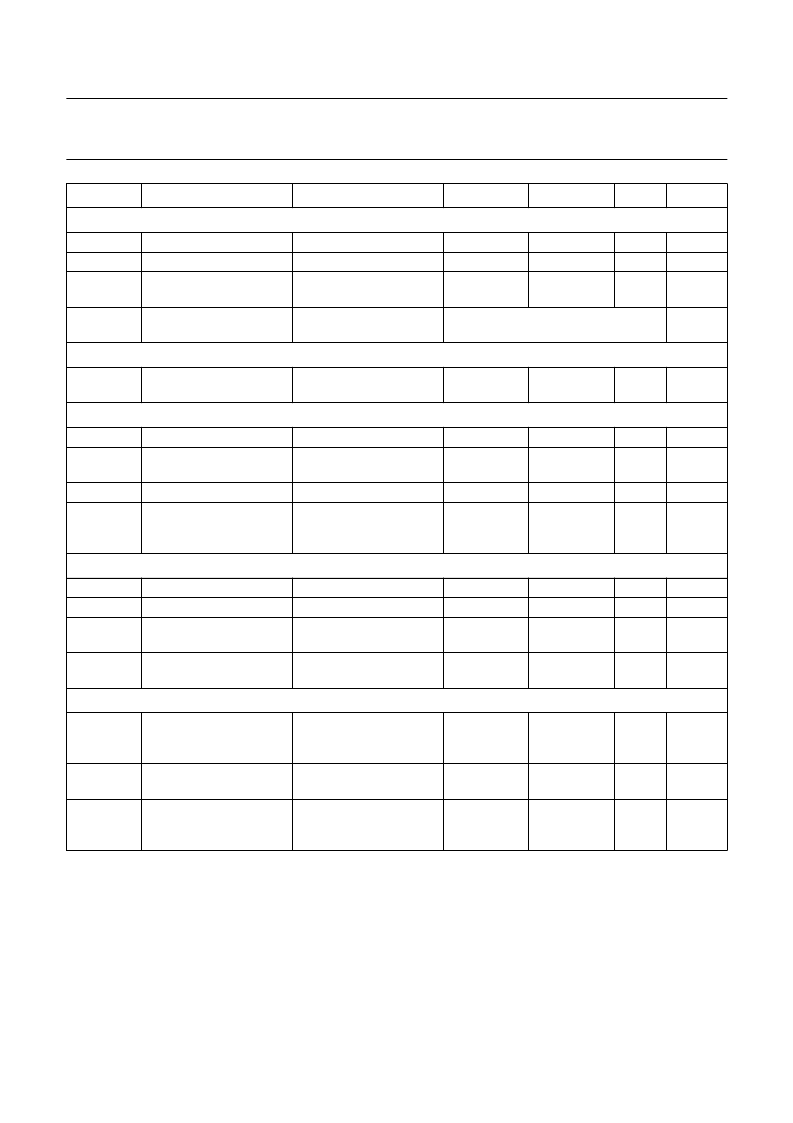

ZIF (I and Q) demodulator

f

offset

t

(ENA-AVG)

t

ENB

offset from 0 frequency

ENA to valid AVG value

ENB to valid

demodulator output

ENB to correct recovered

clock

note 2

3 kHz offset; note 2

note 2

6

100

1

kHz

ms

symbol

duration

t

ENC

note 2

phase error curves apply (see Fig.27)

All outputs

t

r,f

rise and fall times for

outputs

C

L

= 20 pF

15

ns

Open-drain pins SDA and SCL (P1.7 and P1.6)

t

n

V/

t

noise suppression filter

slope for the falling edge

60

50

ns

ns/V

R

L

= 20 k

; C

L

= 50 pF;

V

DD

= 2.2 V

R

L

= 20 k

; C

L

= 50 pF

V

DD

= 2.2 V; R

L

= 20 k

;

C

L

= 50 pF

dI/dt

I

o(sink)(swL)

slope for both edges

dynamic output sink

current during switching

low (Miller compensated)

250

2

μ

A/ns

mA

OTP programming characteristics

V

SU;PP

t

W(prog)

t

W(prog)(sec)

V

PP

set-up time

program pulse width

program pulse security

bits

program pulse recover

time

10

100

200

μ

s

μ

s

μ

s

t

W(prog)(rec)

1

μ

s

AFC-DAC

t

start(DAC)

start-up time disabled

DAC to stable output for

code 111111

power supply ripple

rejection (V

DD

-> DAC)

slew time for analog

output from 10 to 90%

for a voltage step of 1 V

note 2

50

100

μ

s

PSRR

0

dB

t

slew

code 010000 <-> 110000

2.5

μ

s

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCA5010H | Pager baseband controller |

| PCA82C200 | STAND-ALONE CAN-CONTROLLER |

| PCA82C200P | STAND-ALONE CAN-CONTROLLER |

| PCA82C200T | STAND-ALONE CAN-CONTROLLER |

| PCA82C250 | CAN controller interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCA5010H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Pager baseband controller |

| PCA5010H/XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|QFP|48PIN|PLASTIC |

| PCA503HL320 | 制造商:ADAM-TECH 制造商全稱:Adam Technologies, Inc. 功能描述:ZIF FLEX CIRCUIT CONNECTOR |

| PCA503HU320 | 制造商:ADAM-TECH 制造商全稱:Adam Technologies, Inc. 功能描述:ZIF FLEX CIRCUIT CONNECTOR |

| PCA503V320 | 制造商:ADAM-TECH 制造商全稱:Adam Technologies, Inc. 功能描述:ZIF FLEX CIRCUIT CONNECTOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。