- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385408 > HTG2150 (Holtek Semiconductor Inc.) 8-Bit 320 Pixel LCD Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | HTG2150 |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit 320 Pixel LCD Microcontroller |

| 中文描述: | 8位微控制器320像素LCD |

| 文件頁數(shù): | 13/49頁 |

| 文件大小: | 316K |

| 代理商: | HTG2150 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

HTG2150

13

July 24, 2000

Preliminary

Arithmetic and logic unit

ALU

This circuit performs 8-bit arithmetic and logic

operation. The ALU provides the following

functions:

Arithmetic operations (ADD, ADC, SUB,

SBC, DAA)

Logic operations (AND, OR, XOR, CPL)

Rotation (RL, RR, RLC, RRC)

Increment and Decrement (INC, DEC)

Branch decision (SZ, SNZ, SIZ, SDZ ....)

The ALU not only saves the results of a data op-

eration but also changes the status register.

Status register

STATUS

This 8-bit register (0AH) contains the zero flag

(Z), carry flag (C), auxiliary carry flag (AC),

overflow flag (OV), power down flag (PD) and

watchdog time-out flag (TO). It also records the

status information and controls the operation se-

quence.

With the exception of the TO and PD flags, bits

in the status register can be altered by instruc-

tions like any other register. Any data written

into the status register will not change the TO

or PD flags. In addition it should be noted that

operations related to the status register may

give different results from those intended. The

TO and PD flags can only be changed by system

power up, Watchdog Timer overflow, executing

the HALT instruction and clearing the Watch-

dog Timer.

The Z, OV, AC and C flags generally reflect the

status of the latest operations.

In addition, on entering the interrupt sequence

or executing the subroutine call, the status reg-

ister will not be automatically pushed onto the

stack. If the contents of status are important

and if the subroutine can corrupt the status

register, precautions must be taken to save it

properly.

Interrupt

TheHTG2150providesanexternalinterruptand

a PWM D/A interrupt and internal timer inter-

rupts. The Interrupt Control register (INTC;0BH,

INTCH;1EH)containstheinterruptcontrolbitsto

set the enable/disable and the interrupt request

flags.

Once an interrupt subroutine is serviced, all

other interrupts will be blocked (by clearing the

EMI bit). This scheme may prevent any further

interrupt nesting. Other interrupt requests may

happen during this interval but only the inter-

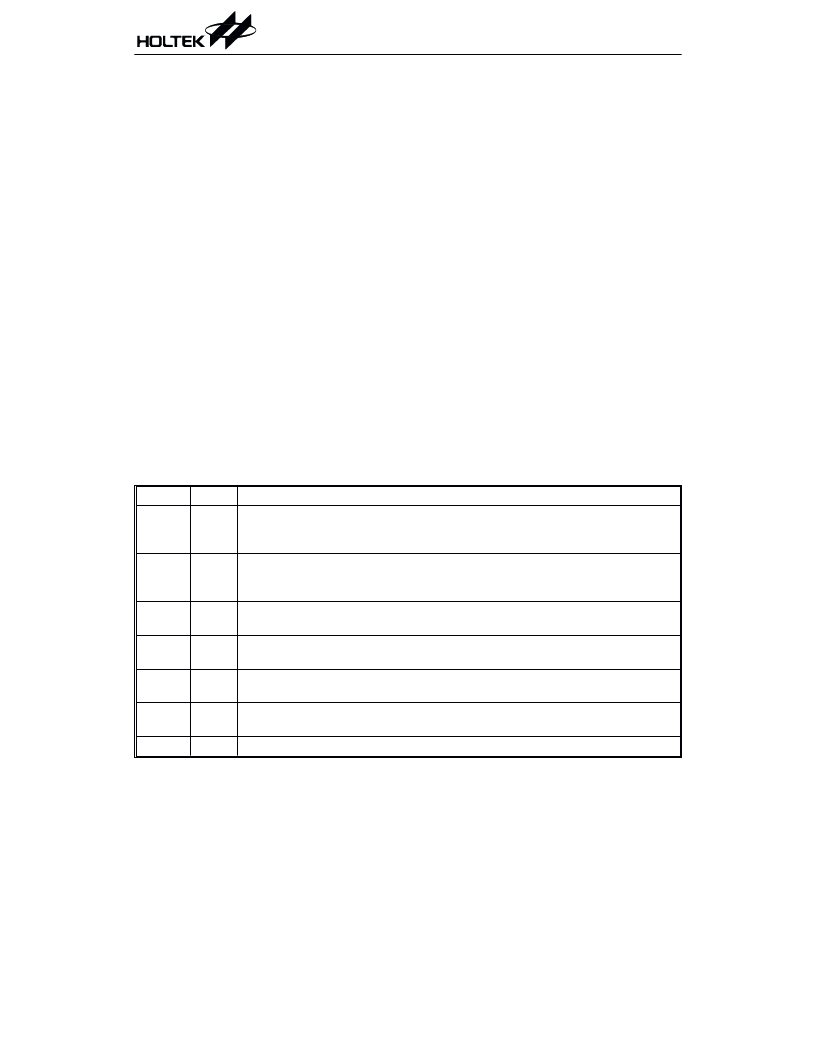

Labels

Bits

Function

C

0

Cissetiftheoperationresultsinacarryduringanadditionoperationorifabor-

row does not take place during a subtraction operation; otherwise C is cleared. C

is also affected by a rotate through carry instruction.

AC

1

ACissetiftheoperationresultsinacarryoutofthelownibblesinadditionorno

borrow from the high nibble into the low nibble in subtraction; otherwise AC is

cleared.

Z

2

Z is set if the result of an arithmetic or logic operation is zero; otherwise Z is

cleared.

OV

3

OV is set if the operation results in a carry into the highest-order bit but not a

carry out of the highest-order bit, or vice versa; otherwise OV is cleared.

PD

4

PD is cleared when either a system powers up or a CLR WDT instruction is exe-

cuted. PD is set by executing the HALT instruction.

TO

5

TO is cleared by a system power-up or executing the CLR WDT or HALT in-

struction. TO is set by a WDT time-out.

6, 7

Undefined bits, read as 0 .

Status register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HTG2190 | 8-Bit 1024 Pixel LCD Microcontroller |

| HTIP117D | PNP EPITAXIAL PLANAR TRANSISTOR |

| HTM1505 | RELATIVE HUMIDITY AND TEMPERATURE MODULE |

| HTM2500 | RELATIVE HUMIDITY/ TEMPERATURE MODULE |

| HTS2010SMD | TEMPERATURE AND RELATIVE HUMIDITY SENSOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HTG2150_02 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit 320 Pixel Dot Matrix LCD MCU Series |

| HTG2170 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| HTG2190 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit 1024 Pixel Dot Matrix LCD MCU Series |

| HTG2190_02 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:8-Bit 1024 Pixel Dot Matrix LCD MCU Series |

| HTG3110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Speech Synthesizer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。