- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383012 > GMS87C7216LQ (Electronic Theatre Controls, Inc.) 8-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | GMS87C7216LQ |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | 數(shù)學(xué)處理器 |

| 英文描述: | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | 8位單晶片微控制器 |

| 文件頁數(shù): | 77/121頁 |

| 文件大小: | 1645K |

| 代理商: | GMS87C7216LQ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當(dāng)前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁

GMS81C7208/7216

FEB. 2005 Ver 1.04

73

19. WATCH / WATCHDOG TIMER

19.1 Watch Timer

The watch timer goes the clock continuously even during the

power saving mode. When MCU is in the Stop or Sleep mode,

MCU can wake up itself every 2Hz or 4Hz or 16Hz.

The watch timer consists of input clock selector, 14-bit binary

counter, interval selector and watch timer mode register WTMR

(address 0EF

H

). The WTMR is 5-bit read/write register and

shown in Figure 19-2. WTMR can select the clock input by 2 bits

WTCK[1:0] and interval time selector by 2 bits WTIN[1:0] and

enable/disable bit. The WTEN bit is set to “1” timer start count-

ing. Input clocks can be selected among three different source

which are divided main clock (f

XIN

÷

128) or main clock. Recom-

mend the oscillator 4.194304MHz as a main. Because above

main frequency is equal to 128 times of 32.768kHz. Generally

main clock (f

XIN

) at WTCK=10

B

is not be used, it is just for test

purpose in factory.

In the Stop Mode, the main clock is stopped.

LDM

EI

LDM

IENL,#XXXX_X1XXB

WTMR,#0100_1000B

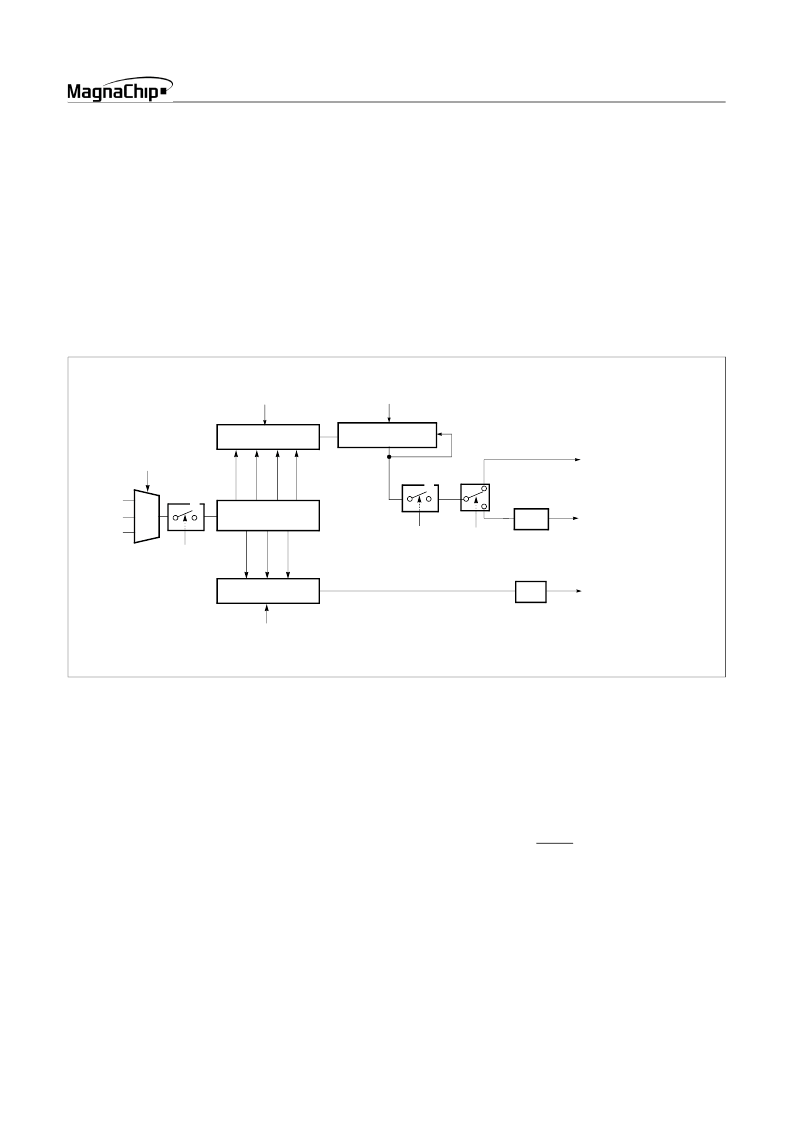

Figure 19-1 Block Diagram of Watchdog Timer

19.2 Watchdog Timer

The watchdog timer rapidly detects the CPU malfunction such as

endless looping caused by noise or the like, and resumes the CPU

to the normal state.

The watchdog timer signal for detecting malfunction can be se-

lected either a reset CPU or a interrupt request as you want.

When the watchdog timer is not being used for malfunction de-

tection, it can be used as a timer to generate an interrupt at fixed

intervals.

Watchdog Timer Control

Figure 19-2 shows the watchdog timer control register WDTR

(address 0DF

H

). The watchdog timer is automatically enabled

initially and watchdog output to reset CPU but clock input source

is disabled. To enable this function, you should write bit WTEN

of WTMR (address 0EF

H

) set to “1”.

The CPU malfunction is detected during setting of the detection

time, selecting of output, and clearing of the binary counter.

Clearing the 2-bit binary counter by bit WDCLR of WDTR is re-

peated within the detection time.

If the malfunction occurs for any cause, the watchdog timer out-

put will become active from the binary counters unless the binary

counter is cleared. At this time, when WDOM=1, a reset is gen-

erated, which drives the RESET pin to low to reset the internal

hardware. When WDOM=0, a watchdog timer interrupt (WD-

TIF) is generated instead of Reset function. This interrupt can be

used general timer as user want.

When main clock is selected as clock input source on the STOP

mode, clock input is stopped so the watchdog timer temporarily

stops counting.

enable

Watch Timer interrupt

WTIF

0

1

14-bit Binary Counter

MUX

11

reserved

f

XIN

÷

128

f

XIN

(test)

f

W

f

XIN

= 4.194304 MHz

Interval Selector

2

4

1

2

4

8

1

2-bit Binary Counter

WDCK[1:0]

WTIN[1:0]

WTCK[1:0]

c

0: Stop

1: Clear and start

WDCLR

WDTIF

to RESET CPU

Watchdog Timer Interrupt

overflow

WDEN

WDOM

00

01

10

00

01

10

00

01

10

enable

0

1

WTEN

MUX

When

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GNR20D101K | VARISTOR |

| GNR20D102K | VARISTOR |

| GNR20D112K | VARISTOR |

| GNR20D121K | VARISTOR |

| GNR20D151K | VARISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GMS87C7216Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GM-S-88 | 功能描述:以太網(wǎng)和電信連接器 8P8C R/A PCB SHIELD LOW PROFILE BLACK RoHS:否 制造商:Pulse 產(chǎn)品:Modular Jacks 性能類別: USOC 代碼:RJ45 位置/觸點數(shù)量: 安裝風(fēng)格:Through Hole 端口數(shù)量:1 x 1 型式:Female 屏蔽: 電流額定值: 電壓額定值: 觸點電鍍: 外殼材料:Thermoplastic IP 等級: |

| GM-S-88-50 | 功能描述:以太網(wǎng)和電信連接器 8P8C R/A PCB SHIELD LOW PROFILE BLK 50u RoHS:否 制造商:Pulse 產(chǎn)品:Modular Jacks 性能類別: USOC 代碼:RJ45 位置/觸點數(shù)量: 安裝風(fēng)格:Through Hole 端口數(shù)量:1 x 1 型式:Female 屏蔽: 電流額定值: 電壓額定值: 觸點電鍍: 外殼材料:Thermoplastic IP 等級: |

| GMS90 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GMS90C31 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR INC. 8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。