- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383012 > GMS87C7216LQ (Electronic Theatre Controls, Inc.) 8-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號(hào): | GMS87C7216LQ |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | 數(shù)學(xué)處理器 |

| 英文描述: | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | 8位單晶片微控制器 |

| 文件頁數(shù): | 56/121頁 |

| 文件大?。?/td> | 1645K |

| 代理商: | GMS87C7216LQ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當(dāng)前第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁

GMS81C7208/7216

52

FEB. 2005 Ver 1.04

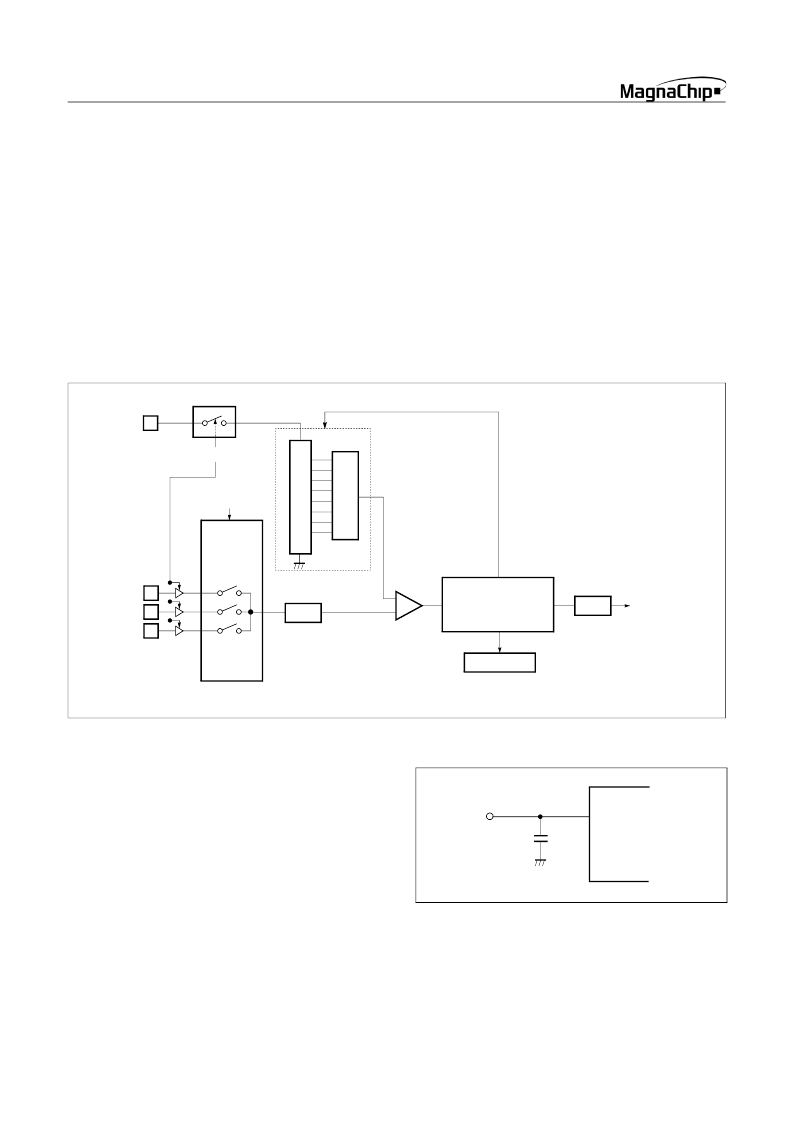

14. ANALOG DIGITAL CONVERTER

The analog-to-digital converter (A/D) allows conversion of an

analog input signal to a corresponding 8-bit digital value. The A/

D module has three analog inputs, which are multiplexed into one

sample and hold. The output of the sample and hold is the input

into the converter, which generates the result via successive ap-

proximation. The analog supply voltage is connected to AV

DD

of

ladder resistance of A/D module.

The A/D module has two registers which are the control register

ADCM and A/D result register ADR. The register ADCM, shown

in Figure 14-4, controls the operation of the A/D converter mod-

ule. The port pins can be configured as analog inputs or digital I/

O. To use analog inputs, I/O is selected input mode by R2DD di-

rection register.

How to Use A/D Converter

The processing of conversion is start when the start bit ADST is

set to “1”. After one cycle, it is cleared by hardware. The register

ADR contains the results of the A/D conversion. When the con-

version is completed, the result is loaded into the ADR, the A/D

conversion status bit ADSF is set to “1”, and the A/D interrupt

flag AIF is set. The block diagram of the A/D module is shown in

Figure 14-1. The A/D status bit ADSF is set automatically when

A/D conversion is completed, cleared when A/D conversion is in

process. The conversion time takes maximum 20 uS (at f

XIN

=4

MHz).

Figure 14-1 A/D Block Diagram

A/D Converter Cautions

(1) Input voltage range of AN1 to AN3

The input voltage of AN1 to AN3 should be within the specifica-

tion range. In particular, if a voltage above AV

DD

or below AV

SS

is input (even if within the absolute maximum rating range), the

conversion value for that channel can not be indeterminate. The

conversion values of the other channels may also be affected.

(2) Noise countermeasures

In order to maintain 8-bit resolution, attention must be paid to

noise on pins AV

DD

and AN1 to AN3. Since the effect increases

in proportion to the output impedance of the analog input source,

it is recommended that a capacitor be connected externally as

shown in Figure 14-2 in order to reduce noise.

.

Figure 14-2 Analog Input Pin Connecting Capacitor

R21/AN1

R22/AN2

R23/AN3

S/H

Sample & Hold

“0”

“1”

ADEN

AV

DD

8

L

ADIF

A/D

INTERRUPT

SUCCESSIVE

APPROXIMATION

CIRCUIT

ADR

A/D result register

ADDRESS: ED

RESET VALUE: Undefined

001

010

011

ADS[2:0]

AN1~AN3

100~1000pF

Analog

Input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GNR20D101K | VARISTOR |

| GNR20D102K | VARISTOR |

| GNR20D112K | VARISTOR |

| GNR20D121K | VARISTOR |

| GNR20D151K | VARISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GMS87C7216Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GM-S-88 | 功能描述:以太網(wǎng)和電信連接器 8P8C R/A PCB SHIELD LOW PROFILE BLACK RoHS:否 制造商:Pulse 產(chǎn)品:Modular Jacks 性能類別: USOC 代碼:RJ45 位置/觸點(diǎn)數(shù)量: 安裝風(fēng)格:Through Hole 端口數(shù)量:1 x 1 型式:Female 屏蔽: 電流額定值: 電壓額定值: 觸點(diǎn)電鍍: 外殼材料:Thermoplastic IP 等級(jí): |

| GM-S-88-50 | 功能描述:以太網(wǎng)和電信連接器 8P8C R/A PCB SHIELD LOW PROFILE BLK 50u RoHS:否 制造商:Pulse 產(chǎn)品:Modular Jacks 性能類別: USOC 代碼:RJ45 位置/觸點(diǎn)數(shù)量: 安裝風(fēng)格:Through Hole 端口數(shù)量:1 x 1 型式:Female 屏蔽: 電流額定值: 電壓額定值: 觸點(diǎn)電鍍: 外殼材料:Thermoplastic IP 等級(jí): |

| GMS90 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GMS90C31 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR INC. 8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。