- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370311 > GCIXF440ACT Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號: | GCIXF440ACT |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 32/128頁 |

| 文件大小: | 1262K |

| 代理商: | GCIXF440ACT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

Intel

IXF1002 Dual Port Gigabit Ethernet Controller

32

Datasheet

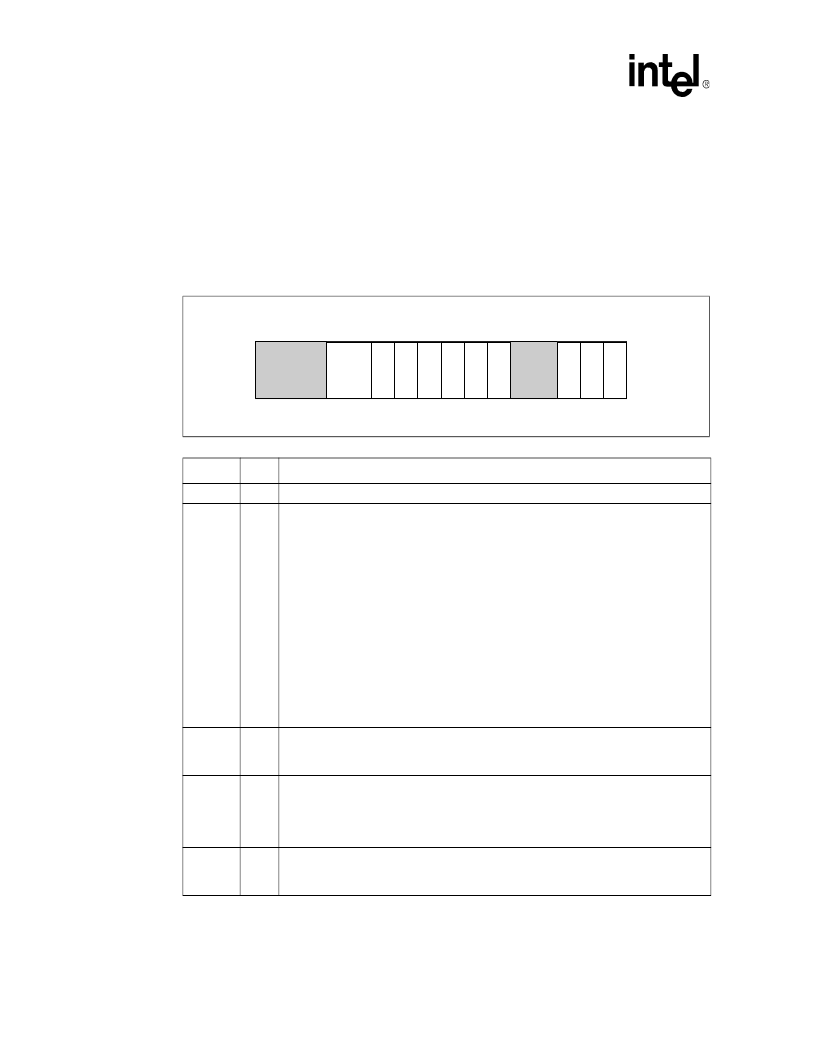

3.2.3.3

Port Working Mode Register

Mnemonic: PORT_MODE

Address: 24H

–

25H

The port mode register controls the CPU bus, IX Bus, and serial interface modes of work.

Note:

Details on Multi-Packet Mode (available with the GCIXF1002ED) are contained in

Appendix C.4

.

Note:

Bits 12, 11, 2, and 0 must have the same value in both ports.

Bit Name

Bit #

Bit Description

—

15:13

RESERVED

FIFMD

12:11

IX Bus mode:

This field sets the IX Bus mode. Both ports of the IXF1002 must be operating in the same

IX Bus mode. The table below shows the IX Bus mode according to bits 12 and 11.

Bit 12

Bit 11

Mode

0

0

Narrow-32 bit mode

0

1

Full-64 bit mode

1

0

Split mode

1

1

Reserved

In the full-64 bit mode, the 64 bits fdat<63:0> are used for either transmitting or receiving

data.

In the split mode, the 32 lower bits fdat<31:0> are used for receiving packets from the

receive FIFO and the 32 higher bits fdat<63:32> are used for transmitting packets to the

transmit FIFO.

In the narrow mode, the lower 32 bits fdat<31:1> are used for either transmitting or

receiving packets.

HRYD

10

Header ready disable.

When set, the

rxrdy

signal will not be asserted when a packet header is in FIFO, but only

according to FIFO threshold values.

PS_D

9

Packet status disable.

When set, the packet status will not be appended to received packets that are transferred

onto the IX Bus. When reset, The packet status is appended to any packet completely

transferred onto the IX Bus, and is driven onto the IX Bus in the access following the last

byte transfer (

see 4.3.1.1

).

BEND

8

Big or little endian mode.

Defines the byte ordering mode on the IX Bus. When set, the port uses the big endian

mode. When reset, the little endian mode is used.

A4975-01

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

H

R

Y

D

P

S

–

D

B

E

N

D

L

C

K

E

F

X

E

C

D

I

L

P

K

F

I

F

M

D

G

P

C

S

S

D

D

I

S

C

P

U

B

W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GCIXP1250-166 | Microprocessor |

| GCIXP1250-200 | Microprocessor |

| GCIXP1250-232 | Microprocessor |

| GCK101 | Analog IC |

| GCK131 | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GCIXP1200EB | 功能描述:IC NETWRK PROCESSR 200MHZ 432BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:SCC 處理器類型:Z380 特點:全靜電 Z380 CPU 速度:20MHz 電壓:5V 安裝類型:表面貼裝 封裝/外殼:144-LQFP 供應(yīng)商設(shè)備封裝:144-LQFP 包裝:托盤 |

| GCIXP1200FC | 功能描述:IC NETWRK PROCESSR 232MHZ 432BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:SCC 處理器類型:Z380 特點:全靜電 Z380 CPU 速度:20MHz 電壓:5V 安裝類型:表面貼裝 封裝/外殼:144-LQFP 供應(yīng)商設(shè)備封裝:144-LQFP 包裝:托盤 |

| GCIXP1200GA | 功能描述:IC MPU NETWORK 166MHZ 432-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:SCC 處理器類型:Z380 特點:全靜電 Z380 CPU 速度:20MHz 電壓:5V 安裝類型:表面貼裝 封裝/外殼:144-LQFP 供應(yīng)商設(shè)備封裝:144-LQFP 包裝:托盤 |

| GCIXP1200GB | 功能描述:IC MPU NETWORK 200MHZ 432-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點:- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCIXP1200GC | 功能描述:IC MPU NETWORK 232MHZ 432-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點:- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。