- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223311 > ADSP-TS203SABPZ050 (ANALOG DEVICES INC) 500 MHz TigerSHARC Processor with 4 Mbit on-chip embedded DRAM; Package: 576 ball SBGA; No of Pins: 576; Temperature Range: Ind PDF資料下載

參數(shù)資料

| 型號: | ADSP-TS203SABPZ050 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 500 MHz TigerSHARC Processor with 4 Mbit on-chip embedded DRAM; Package: 576 ball SBGA; No of Pins: 576; Temperature Range: Ind |

| 中文描述: | 32-BIT, 125 MHz, OTHER DSP, PBGA576 |

| 封裝: | 25 X 25 MM, MS-034, BGA-576 |

| 文件頁數(shù): | 2/48頁 |

| 文件大小: | 2017K |

| 代理商: | ADSP-TS203SABPZ050 |

第1頁當前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

Rev. C

|

Page 10 of 48

|

December 2006

ADSP-TS203S

POWER DOMAINS

The ADSP-TS203S processor has separate power supply con-

nections for internal logic (VDD), analog circuits (VDD_A), I/O

buffer (VDD_IO), and internal DRAM (VDD_DRAM) power supply.

Note that the analog (VDD_A) supply powers the clock generator

PLLs. To produce a stable clock, systems must provide a clean

power supply to power input VDD_A. Designs must pay critical

attention to bypassing the VDD_A supply.

FILTERING REFERENCE VOLTAGE AND CLOCKS

and SCLK_VREF. These circuits provide the reference voltages

for the switching voltage reference and system clock reference.

DEVELOPMENT TOOLS

The ADSP-TS203S processor is supported with a complete set

of CROSSCORE

software and hardware development tools,

including Analog Devices emulators and VisualDSP++

devel-

opment environment. The same emulator hardware that

supports other TigerSHARC processors also fully emulates the

ADSP-TS203S processor.

The VisualDSP++ project management environment lets pro-

grammers develop and debug an application. This environment

includes an easy to use assembler (which is based on an alge-

braic syntax), an archiver (librarian/library builder), a linker, a

loader, a cycle-accurate instruction-level simulator, a C/C++

compiler, and a C/C++ run-time library that includes DSP and

mathematical functions. A key point for theses tools is C/C++

code efficiency. The compiler has been developed for efficient

translation of C/C++ code to DSP assembly. The DSP has archi-

tectural features that improve the efficiency of compiled

C/C++ code.

The VisualDSP++ debugger has a number of important

features. Data visualization is enhanced by a plotting package

that offers a significant level of flexibility. This graphical

representation of user data enables the programmer to quickly

determine the performance of an algorithm. As algorithms grow

in complexity, this capability can have increasing significance

on the designer’s development schedule, increasing productiv-

ity. Statistical profiling enables the programmer to

nonintrusively poll the processor as it is running the program.

This feature, unique to VisualDSP++, enables the software

developer to passively gather important code execution metrics

without interrupting the real-time characteristics of the

program. Essentially, the developer can identify bottlenecks in

software quickly and efficiently. By using the profiler, the pro-

grammer can focus on those areas in the program that impact

performance and take corrective action.

Debugging both C/C++ and assembly programs with the

VisualDSP++ debugger, programmers can:

View mixed C/C++ and assembly code (interleaved source

and object information)

Insert breakpoints

Set conditional breakpoints on registers, memory,

and stacks

Trace instruction execution

Perform linear or statistical profiling of program execution

Fill, dump, and graphically plot the contents of memory

Perform source level debugging

Create custom debugger windows

The VisualDSP++ IDE lets programmers define and manage

DSP software development. Its dialog boxes and property pages

let programmers configure and manage all of the TigerSHARC

processor development tools, including the color syntax high-

lighting in the VisualDSP++ editor. This capability permits

programmers to:

Control how the development tools process inputs and

generate outputs

Maintain a one-to-one correspondence with the tool’s

command line switches

The VisualDSP++ Kernel (VDK) incorporates scheduling and

resource management tailored specifically to address the mem-

ory and timing constraints of DSP programming. These

capabilities enable engineers to develop code more effectively,

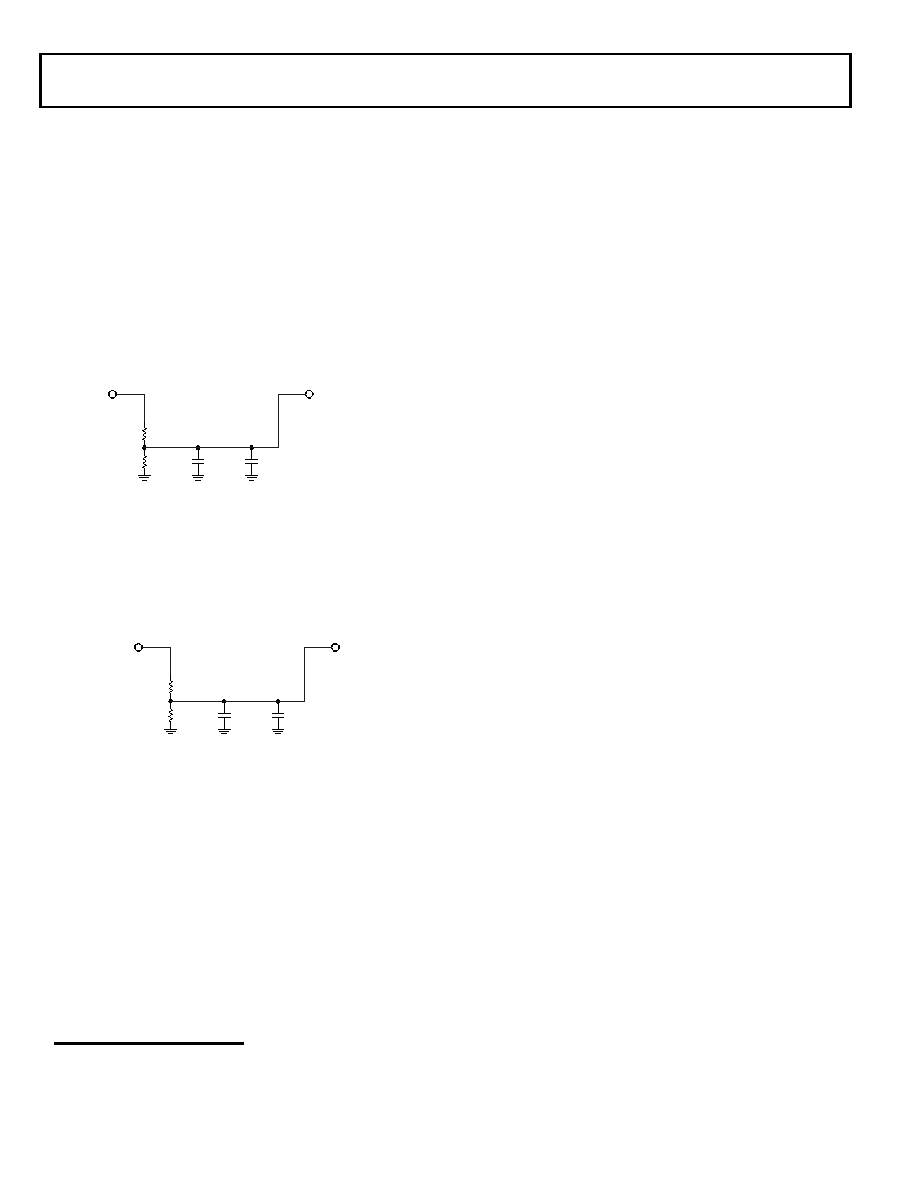

Figure 6. VREF Filtering Scheme

Figure 7. SCLK_VREF Filtering Scheme

CROSSCORE is a registered trademark of Analog Devices, Inc.

VisualDSP++ is a registered trademark of Analog Devices, Inc.

VDD_IO

VSS

VREF

R1

R2

C1

C2

R1: 2k

SERIES RESISTOR (±1%)

R2: 2.55k

SERIES RESISTOR (±1%)

C1: 1 F CAPACITOR (SMD)

C2: 1nF CAPACITOR (HF SMD) PLACED CLOSE TO DSP’S PINS

CLOCK DRIVER

VOLTAGE OR

VDD_IO

VSS

SCLK_VREF

R1

R2

C1

C2

R1: 2k

SERIES RESISTOR (±1%)

R2: 2.55k

SERIES RESISTOR (±1%)

C1: 1 F CAPACITOR (SMD)

C2: 1nF CAPACITOR (HF SMD) PLACED CLOSE TO DSP’S PINS

*IF CLOCK DRIVER VOLTAGE > V

DD_IO

*

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSQ-1410-EX-C | 4-CH 14-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, DMA66 |

| ADT-2734-MM-35M-02 | MALE-MALE, RF STRAIGHT ADAPTER, PLUG |

| ADT-2744-MM-HNO-02 | MALE-MALE, RF STRAIGHT ADAPTER, PLUG |

| ADT-2779-TF-SMF-00 | PANEL MOUNT, FEMALE, RF STRAIGHT ADAPTER |

| ADT-2802-7M-HNF-02 | MALE-FEMALE, RF STRAIGHT ADAPTER, JACK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-TS203SBBPZ050 | 制造商:Analog Devices 功能描述:DSP - Bulk |

| ADSQ-1410 | 制造商:MURATA-PS 制造商全稱:Murata Power Solutions Inc. 功能描述:Quad 14-Bit, 10 MSPS Sampling A/D Converter |

| ADSQ-1410-C | 制造商:MURATA-PS 制造商全稱:Murata Power Solutions Inc. 功能描述:Quad 14-Bit, 10 MSPS Sampling A/D Converter |

| ADSQ-1410-EX-C | 制造商:MURATA-PS 制造商全稱:Murata Power Solutions Inc. 功能描述:Quad 14-Bit, 10 MSPS Sampling A/D Converter |

| ADSQ-1410S | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 0 to 70C 66-pin DIP Quad 14-Bit, 10MPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復。