- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223307 > ADE7878ACPZ (ANALOG DEVICES INC) Poly Phase Multifunction Energy Metering IC With Total And Fundamental Powers, No Of Pins: 40, Temperature Range: Ind PDF資料下載

參數(shù)資料

| 型號(hào): | ADE7878ACPZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 英文描述: | Poly Phase Multifunction Energy Metering IC With Total And Fundamental Powers, No Of Pins: 40, Temperature Range: Ind |

| 中文描述: | SPECIALTY ANALOG CIRCUIT, QCC40 |

| 封裝: | 6 X 6 MM, ROHS COMPLIANT, MO-220WJJD, LFCSP-40 |

| 文件頁(yè)數(shù): | 87/96頁(yè) |

| 文件大小: | 1096K |

| 代理商: | ADE7878ACPZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)當(dāng)前第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)

ADE7854/ADE7858/ADE7868/ADE7878

Rev. E| Page 88 of 96

Bit

Location

Bit Mnemonic

Default Value

Description

12

CF1LATCH

0

When this bit is set to 1, the content of the corresponding energy registers is latched when a

CF1 pulse is generated. See the Synchronizing Energy Registers with CFx Outputs section.

13

CF2LATCH

0

When this bit is set to 1, the content of the corresponding energy registers is latched when a

CF2 pulse is generated. See the Synchronizing Energy Registers with CFx Outputs section.

14

CF3LATCH

0

When this bit is set to 1, the content of the corresponding energy registers is latched when a

CF3 pulse is generated. See the Synchronizing Energy Registers with CFx Outputs section.

15

Reserved

0

Reserved. This bit does not manage any functionality.

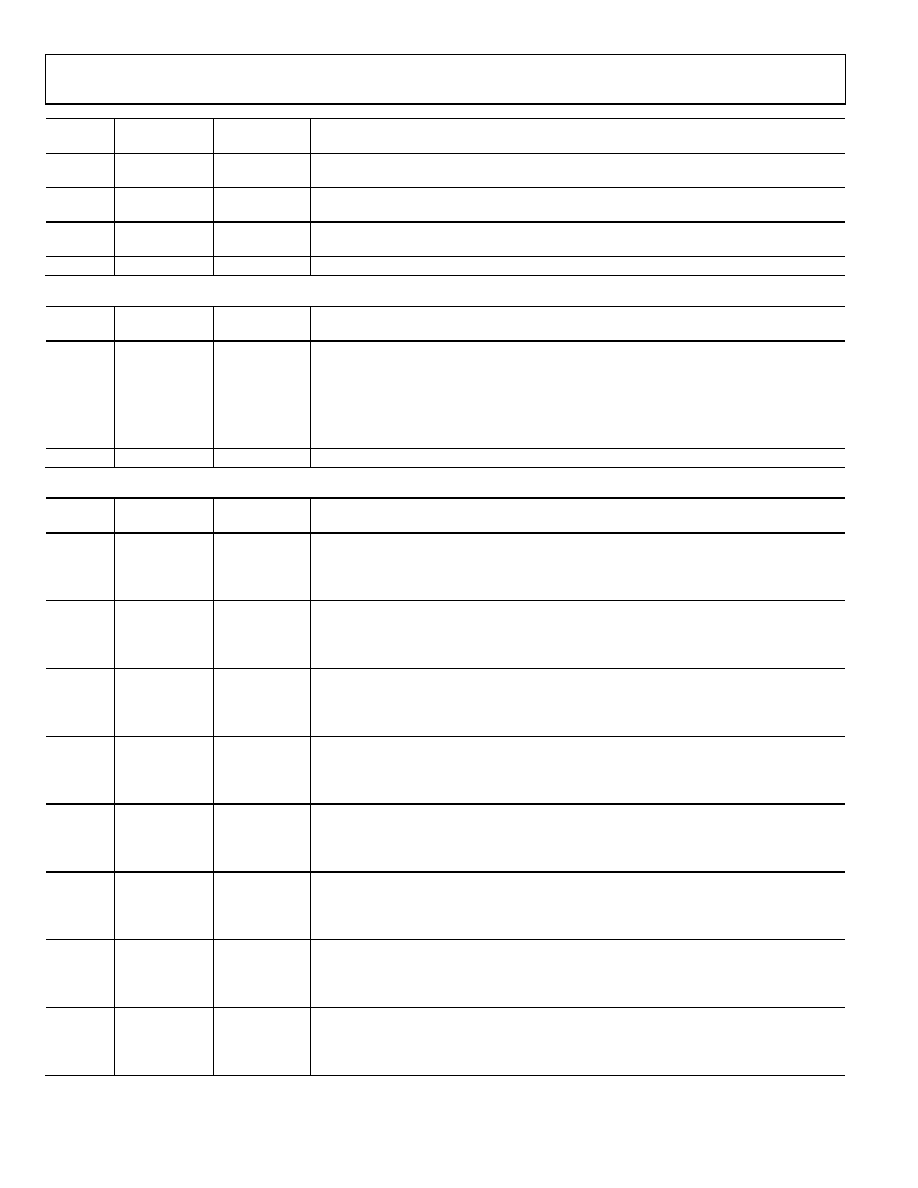

Table 46. APHCAL, BPHCAL, CPHCAL Registers (Address 0xE614, Address 0xE615, Address 0xE616)

Bit

Location

Bit Mnemonic

Default Value

Description

If current channel compensation is necessary, these bits can vary only between 0 and 383.

If voltage channel compensation is necessary, these bits can vary only between 512 and 575.

If the PHCALVAL bits are set with numbers between 384 and 511, the compensation behaves

like PHCALVAL set between 256 and 383.

9:0

PHCALVAL

0000000000

If the PHCALVAL bits are set with numbers between 576 and 1023, the compensation

behaves like PHCALVAL bits set between 384 and 511.

15:10

Reserved

000000

Reserved. These bits do not manage any functionality.

Table 47. PHSIGN Register (Address 0xE617)

Bit

Location

Bit Mnemonic

Default Value

Description

0: if the active power identified by Bit 6 (REVAPSEL) in the ACCMODE register (total of

fundamental) on Phase A is positive.

0

AWSIGN

0

1: if the active power identified by Bit 6 (REVAPSEL) in the ACCMODE register (total of

fundamental) on Phase A is negative.

1

BWSIGN

0

0: if the active power identified by Bit 6 (REVAPSEL) in the ACCMODE register (total of

fundamental) on Phase B is positive.

1: if the active power identified by Bit 6 (REVAPSEL) in the ACCMODE register (total of

fundamental) on Phase B is negative.

2

CWSIGN

0

0: if the active power identified by Bit 6 (REVAPSEL) in the ACCMODE register (total of

fundamental) on Phase C is positive.

1: if the active power identified by Bit 6 (REVAPSEL) bit in the ACCMODE register (total of

fundamental) on Phase C is negative.

3

SUM1SIGN

0

0: if the sum of all phase powers in the CF1 datapath is positive.

1: if the sum of all phase powers in the CF1 datapath is negative. Phase powers in the CF1

datapath are identified by Bits[2:0] (TERMSEL1[x]) of the COMPMODE register and by

Bits[2:0] (CF1SEL[x]) of the CFMODE register.

4

AVARSIGN

0

0: if the reactive power identified by Bit 7 (REVRPSEL) in the ACCMODE register (total of

fundamental) on Phase A is positive. This bit is always 0 for ADE7854.

1: if the reactive power identified by Bit 7 (REVRPSEL) in the ACCMODE register (total of

fundamental) on Phase A is negative.

5

BVARSIGN

0

0: if the reactive power identified by Bit 7 (REVRPSEL) in the ACCMODE register (total of

fundamental) on Phase B is positive. This bit is always 0 for ADE7854.

1: if the reactive power identified by Bit 7 (REVRPSEL) in the ACCMODE register (total of

fundamental) on Phase B is negative.

6

CVARSIGN

0

0: if the reactive power identified by Bit 7 (REVRPSEL) in the ACCMODE register (total of

fundamental) on Phase C is positive. This bit is always 0 for ADE7854.

1: if the reactive power identified by Bit 7 (REVRPSEL) in the ACCMODE register (total of

fundamental) on Phase C is negative.

7

SUM2SIGN

0

0: if the sum of all phase powers in the CF2 datapath is positive.

1: if the sum of all phase powers in the CF2 datapath is negative. Phase powers in the CF2

datapath are identified by Bits[5:3] (TERMSEL2[x]) of the COMPMODE register and by

Bits[5:3] (CF2SEL[x]) of the CFMODE register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADE7878ACPZ-RL | Poly Phase Multifunction Energy Metering IC With Total And Fundamental Powers, No Of Pins: 40, Temperature Range: Ind |

| ADG529FTQ | 4-CHANNEL, DIFFERENTIAL MULTIPLEXER, CDIP18 |

| ADJ24006 | POWER/SIGNAL RELAY, SPST, LATCHED, 0.042A (COIL), 6VDC (COIL), 250mW (COIL), THROUGH HOLE-STRAIGHT MOUNT |

| ADJ24012 | POWER/SIGNAL RELAY, SPST, LATCHED, 0.021A (COIL), 12VDC (COIL), 250mW (COIL), THROUGH HOLE-STRAIGHT MOUNT |

| ADJ24024 | POWER/SIGNAL RELAY, SPST, LATCHED, 0.01A (COIL), 24VDC (COIL), 250mW (COIL), THROUGH HOLE-STRAIGHT MOUNT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADE7878ACPZ | 制造商:Analog Devices 功能描述:IC MULTIFUNCTION ENERGY METERING LFCSP40 |

| ADE7878ACPZ-RL | 功能描述:IC ENERGY METERING 3PH 40LFCSP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測(cè)量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

| ADE7878XCPZ | 制造商:Analog Devices 功能描述:POLY PHASE MULTIFUNCTION ENERGY METERING IC WITH TOTAL - Bulk |

| ADE7880 | 制造商:Analog Devices 功能描述:BOARD EVAL ENERGY METER ADE |

| ADE7880ACPZ | 功能描述:IC ENERGY METERING 3PH 40LFCSP RoHS:是 類別:集成電路 (IC) >> PMIC - 能量測(cè)量 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:* |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。