- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1894 > AD9858BSVZ (Analog Devices Inc)IC DDS DAC 10BIT 1GSPS 100-TQFP PDF資料下載

參數(shù)資料

| 型號: | AD9858BSVZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 15/32頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DDS DAC 10BIT 1GSPS 100-TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 設(shè)計資源: | Low Jitter Sampling Clock Generator for High Performance ADCs Using AD9958/9858 and AD9515 (CN0109) |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 分辨率(位): | 10 b |

| 主 fclk: | 1GHz |

| 調(diào)節(jié)字寬(位): | 32 b |

| 電源電壓: | 3.14 V ~ 3.47 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP-EP(14x14) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 552 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD9858

Rev. C | Page 22 of 32

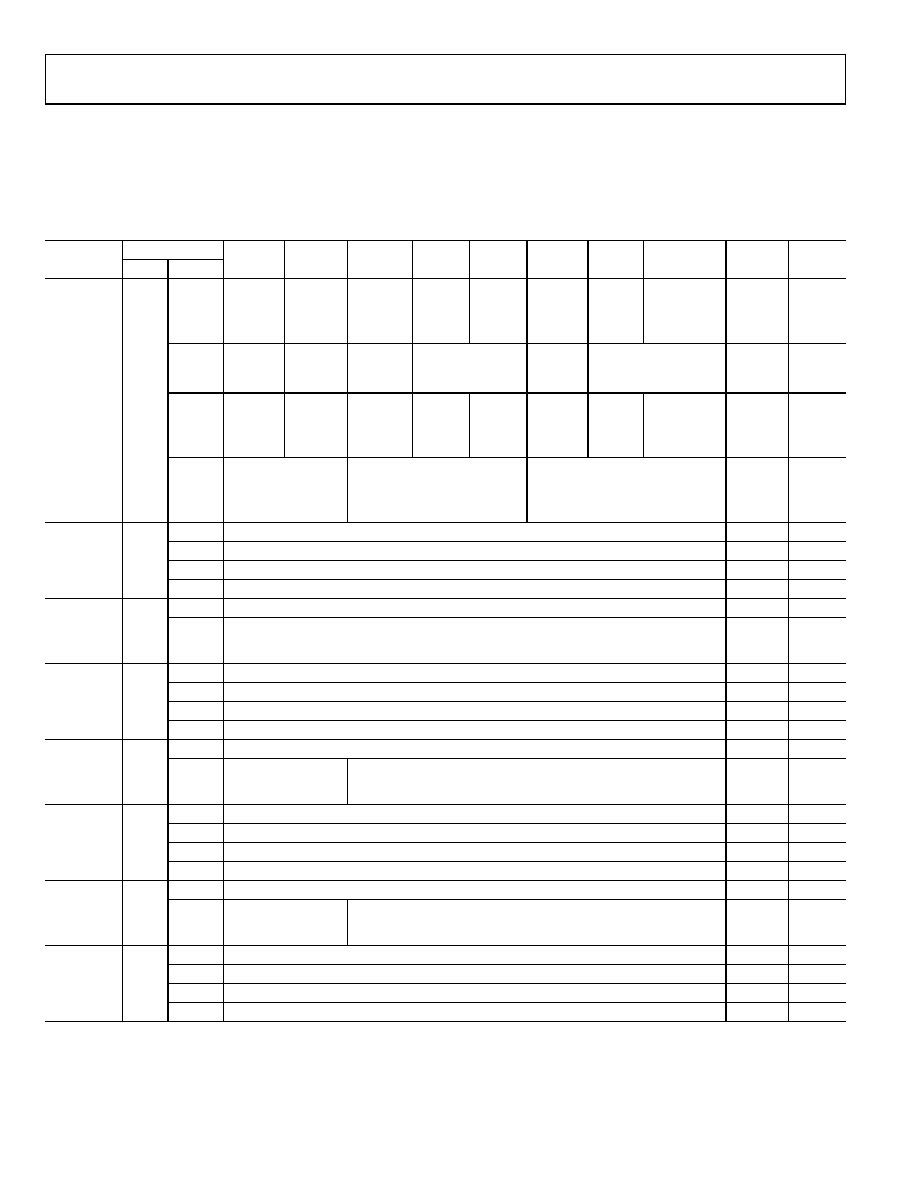

REGISTER MAP

The registers are listed in Table 6. The serial address and parallel address numbers associated with each of the registers are shown in

hexadecimal format. Square brackets [] are used to reference specific bits or ranges of bits. For example, [3] designates Bit 3, and [7:3]

designates the range of bits from 7 down to 3, inclusive.

Table 6.

Register

Address

(MSB)

(LSB)

Default

Name

Ser

Par

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value

Profile

Control

function

register

(CFR)

0x00

[7:0]

Not

used

2 GHz

divider

disable

SYNCLK

disable

Mixer

power-

down

Phase

detect

power-

down

Power-

down

SDIO

input

only

LSB first

0x18

N/A

0x01

[15:8]

Freq.

sweep

enable

Enable

sine

output

Charge

pump

offset

Phase detector

divider ratio (N)

(see Table 10)

Charge

pump

polarity

Phase detector

divider ratio (M)

(see Table 11)

0x00

N/A

0x02

[23:16]

Auto Clr

freq.

accum

Auto Clr

phase

accum

Load

delta

freq

timer

Clear

freq

accum

Clear

phase

accum

Not

used

Fast

lock

enable

FTW for

fast lock

0x00

N/A

0x03

[31:24]

Frequency detect

mode charge

pump current

(see Table 7)

Final closed-loop

mode charge pump current

(see Table 8)

Wide closed-loop mode

charge pump current

(see Table 9)

0x00

N/A

Delta freq.

tuning

word

(DFTW)

0x01

0x04

Delta Frequency Word[7:0]

N/A

0x05

Delta Frequency Word[15:8]

N/A

0x06

Delta Frequency Word[23:16]

N/A

0x07

Delta Frequency Word[31:24]

N/A

Delta

frequency

ramp rate

(DFRRW)

0x02

0x08

Delta Frequency Ramp Rate Word[7:0]

N/A

0x09

Delta Frequency Ramp Rate Word[15:8]

N/A

Frequency

Tuning

Word 0

(FTW0)

0x03

0x0A

Frequency Tuning Word 0[7:0]

0x00

0

0x0B

Frequency Tuning Word 0[15:8]

0x00

0

0x0C

Frequency Tuning Word 0[23:16]

0x00

0

0x0D

Frequency Tuning Word 0[31:24]

0x00

0

Phase

Offset

Word 0

(POW0)

0x04

0x0E

Phase Offset Word 0[7:0]

0x00

0

0x0F

Not used

Phase Offset Word 0[13:8]

0x00

0

Frequency

Tuning

Word 1

(FTW1)

0x05

0x10

Frequency Tuning Word 1[7:0]

1

0x11

Frequency Tuning Word 1[15:8]

1

0x12

Frequency Tuning Word 1[23:16]

1

0x13

Frequency Tuning Word 1[31:24]

1

Phase

Offset

Word 1

(POW1)

0x06

0x14

Phase Offset Word 1[7:0]

1

0x15

Not used

Phase Offset Word 1[13:8]

1

Frequency

Tuning

Word 2

(FTW2)

0x07

0x16

Frequency Tuning Word 2[7:0]

2

0x17

Frequency Tuning Word 2[15:8]

2

0x18

Frequency Tuning Word 2[23:16]

2

0x19

Frequency Tuning Word 2[31:24]

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9859YSVZ-REEL7 | IC DDS DAC 10BIT 400MSPS 48TQFP |

| AD9880KSTZ-100 | IC INTERFACE/HDMI 100MHZ 100LQFP |

| AD9882KSTZ-140 | IC INTERFACE/DVI 100MHZ 100LQFP |

| AD9883ABSTZ-RL140 | IC INTERFACE FLAT 140MHZ 80LQFP |

| AD9887AKSZ-100 | IC INTRFACE ANALOG/DVI 160-MQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9858FDPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858TLPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858XSV | 制造商:Analog Devices 功能描述: |

| AD9859 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。