- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1894 > AD9858BSVZ (Analog Devices Inc)IC DDS DAC 10BIT 1GSPS 100-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | AD9858BSVZ |

| 廠商: | Analog Devices Inc |

| 文件頁(yè)數(shù): | 10/32頁(yè) |

| 文件大小: | 0K |

| 描述: | IC DDS DAC 10BIT 1GSPS 100-TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Direct Digital Synthesis Tutorial Series (1 of 7): Introduction Direct Digital Synthesizer Tutorial Series (7 of 7): DDS in Action Direct Digital Synthesis Tutorial Series (3 of 7): Angle to Amplitude Converter Direct Digital Synthesis Tutorial Series (6 of 7): SINC Envelope Correction Direct Digital Synthesis Tutorial Series (4 of 7): Digital-to-Analog Converter Direct Digital Synthesis Tutorial Series (2 of 7): The Accumulator |

| 設(shè)計(jì)資源: | Low Jitter Sampling Clock Generator for High Performance ADCs Using AD9958/9858 and AD9515 (CN0109) |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 分辨率(位): | 10 b |

| 主 fclk: | 1GHz |

| 調(diào)節(jié)字寬(位): | 32 b |

| 電源電壓: | 3.14 V ~ 3.47 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP-EP(14x14) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁(yè)面: | 552 (CN2011-ZH PDF) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

AD9858

Rev. C | Page 18 of 32

A DFRRW value of 0 written to the register stops all frequency

sweeping. There is no automated stop-at-a-given-frequency

function. The user must calculate the time interval required to

reach the final frequency and then issue a command to write 0

into the DFRRW register. The time required for a frequency

sweep is calculated by

DFTW

DFRRW

SYSCLK

2

f

t

2

34

S

F

×

=

where:

T is the duration of the sweep in seconds.

fS is the starting frequency determined by

SYSCLK

2

FTW

f

32

S

×

=

fF is the final frequency.

The delta frequency step size is given by

31

2

SYSCLK

DFTW ×

=

Δf

,

remembering that DFTW is a signed (twos complement) value.

The time between each frequency step (Δt) is given by

SYSCLK

DFRRW

×

= 8

Δt

The value of the stop frequency fF is determined by

Δt

Δf

×

+

=

t

f

S

F

Returning to Starting Frequency

The original frequency tuning word (FTW), which is written into

the frequency tuning register, does not change at any time during

a sweep operation. This means that the DDS can return to the

sweep starting frequency at any time during a sweep. Setting the

control bit, autoclear frequency accumulator, forces the frequency

accumulator to 0, instantly returning the DDS to the frequency

stored as FTW.

Full Sleep Mode

Setting all of the power-down bits in the control function register

activates full sleep mode. During the power-down condition,

the clocks associated with the various functional blocks of the

device are turned off, thereby offering a significant power savings.

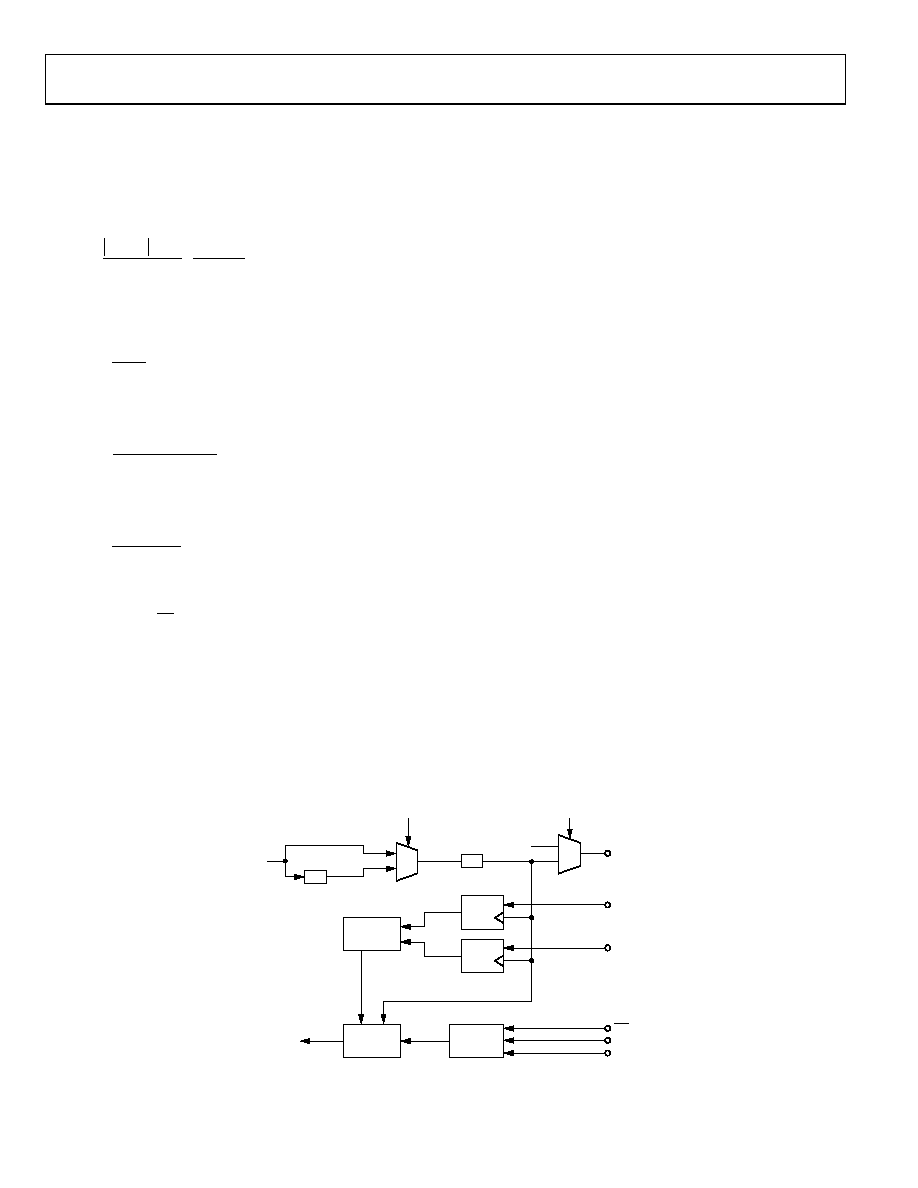

SYNCHRONIZATION

SYNCLK and FUD Pins

Timing for the AD9858 is provided via the user-supplied REFCLK

input. The REFCLK input is buffered and is the source for the

internally generated SYSCLK. The frequency of SYSCLK can be

either the same as REFCLK or half that of REFCLK (CFR[6]).

The REFCLK input is capable of handling input frequencies as

high as 2 GHz. However, the device is designed for a maximum

SYSCLK frequency of 1 GHz. Thus, it is mandatory that the

divide-by-2 SYSCLK function be enabled when the frequency

of REFCLK is greater than 1 GHz.

SYSCLK serves as the sample clock for the DAC and is fed to

a divide-by-8 frequency divider to produce SYNCLK. SYNCLK

is provided to the user on the SYNCLK pin. This enables

synchronization of external hardware with the internal DDS

clock of the AD9858. External hardware that is synchronized

to the SYNCLK signal can then be used to provide the frequency

update (FUD) signal to the AD9858. The FUD signal and

SYNCLK are used to transfer the internal buffer register

contents into the memory registers of the device. Figure 33

shows a block diagram of the synchronization methodology,

and Figure 34 shows an I/O synchronization timing diagram.

SYNCLK is also used to synchronize the assertion of the profile

select pins (PS0 and PS1). The FUD, PS0, and PS1 pins must be

set up and held around the rising edge of SYNCLK.

U

P

DA

T

E

RE

G

S

REGISTER

MEMORY

EDGE

DETECTION

LOGIC

REFCLK

PS0, PS1

FUD

SYNCLK

SYSCLK

0

2 GHz DIVIDER

DISABLE

SYNCLK

DISABLE

TO CORE LOGIC

BUFFER

MEMORY

÷ 2

10

D

Q

WR/SCLK

ADDRx

DATA

SYNCLK

D

Q

÷ 8

03

16

6-

03

6

Figure 33. I/O Synchronization Block Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9859YSVZ-REEL7 | IC DDS DAC 10BIT 400MSPS 48TQFP |

| AD9880KSTZ-100 | IC INTERFACE/HDMI 100MHZ 100LQFP |

| AD9882KSTZ-140 | IC INTERFACE/DVI 100MHZ 100LQFP |

| AD9883ABSTZ-RL140 | IC INTERFACE FLAT 140MHZ 80LQFP |

| AD9887AKSZ-100 | IC INTRFACE ANALOG/DVI 160-MQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9858FDPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858PCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858TLPCB | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 GSPS Direct Digital Synthesizer |

| AD9858XSV | 制造商:Analog Devices 功能描述: |

| AD9859 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MSPS, 10-Bit, 1.8 V CMOS Direct Digital Synthesizer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。