- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382783 > μPD30100 (NEC Corp.) 64-bit RISC Microprosessor(64位 RISC 微處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | μPD30100 |

| 廠商: | NEC Corp. |

| 英文描述: | 64-bit RISC Microprosessor(64位 RISC 微處理器) |

| 中文描述: | 64位RISC Microprosessor(64位的RISC微處理器) |

| 文件頁數(shù): | 34/52頁 |

| 文件大?。?/td> | 365K |

| 代理商: | ΜPD30100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

34

μ

PD30100

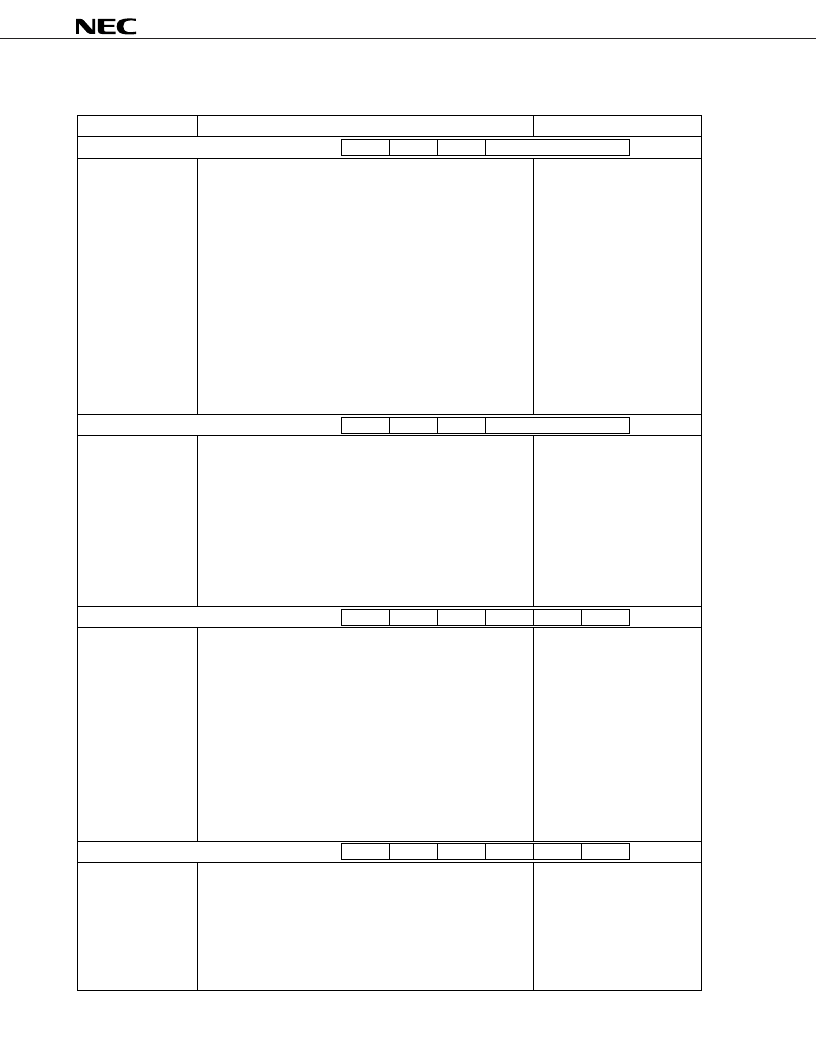

Table 6-1. CPU Instruction Set: ISA (1/3)

op

base

rt

offset

Instructions

Description

Format

Load/store instruction

LB

Load Byte

LB

rt, offset (base)

LBU

Load Byte Unsigned

LBU

rt, offset (base)

LH

Load Halfword

LH

rt, offset (base)

LHU

Load Halfword Unsigned

LHU

rt, offset (base)

LW

Load Word

LW

rt, offset (base)

LWL

Load Word Left

LWL

rt, offset (base)

LWR

Load Word Right

LWR

rt, offset (base)

SB

Store Byte

SB

rt, offset (base)

SH

Store Halfword

SH

rt, offset (base)

SW

Store Word

SW

rt, offset (base)

SWL

Store Word Left

SWL

rt, offset (base)

SWR

Store Word Right

SWR

rt, offset (base)

ALU immediate instruction

ADDI

Add Immediate

ADDI

rt, rs, immediate

ADDIU

Add Immediate Unsigned

ADDIU

rt, rs, immediate

SLTI

Set On Less Than Immediate

SLTI

rt, rs, immediate

SLTIU

Set On Less Than Immediate Unsigned

SLTIU

rt, rs, immediate

ANDI

And Immediate

ANDI

rt, rs, immediate

ORI

Or Immediate

ORI

rt, rs, immediate

XORI

Exclusive Or Immediate

XORI

rt, rs, immediate

LUI

Load Upper Immediate

LUI

rt, immediate

3-operand type instruction

ADD

Add

ADD

rd, rs, rt

ADDU

Add Unsigned

ADDU

rd, rs, rt

SUB

Subtract

SUB

rd, rs, rt

SUBU

Subtract Unsigned

SUBU

rd, rs, rt

SLT

Set On Less Than

SLT

rd, rs, rt

SLTU

Set On Less Than Unsigned

SLTU

rd, rs, rt

AND

And

AND

rd, rs, rt

OR

Or

OR

rd, rs, rt

XOR

Exclusive Or

XOR

rd, rs, rt

NOR

Nor

NOR

rd, rs, rt

Shift instruction

SLL

Shift Left Logical

SLL

rd, rt, sa

SRL

Shift Right Logical

SRL

rd, rt, sa

SRA

Shift Right Arithmetic

SRA

rd, rt, sa

SLLV

Shift Left Logical Variable

SLLV

rd, rt, rs

SRLV

Shift Right Logical Variable

SRLV

rd, rt, rs

SRAV

Shift Right Arithmetic Variable

SRAV

rd, rt, rs

op

rs

rt

rd

sa

funct

op

rs

rt

rd

sa

funct

op

rs

rt

offset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD30101 | 64-Bit Microprocessor(64位微處理器) |

| μPD30102 | 64-/32-BIT Microprocessor(64/32位微處理器) |

| μPD30121 | 64-Bit MIPS RISC Microprocessor(64 位RISC 微處理器) |

| μPD30122 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

| μPD30181 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD301-024-03-PC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| PD301-024-03-P-C-200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-P-C-250 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-P-C-300 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-PI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。