- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382783 > μPD30100 (NEC Corp.) 64-bit RISC Microprosessor(64位 RISC 微處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | μPD30100 |

| 廠商: | NEC Corp. |

| 英文描述: | 64-bit RISC Microprosessor(64位 RISC 微處理器) |

| 中文描述: | 64位RISC Microprosessor(64位的RISC微處理器) |

| 文件頁(yè)數(shù): | 26/52頁(yè) |

| 文件大?。?/td> | 365K |

| 代理商: | ΜPD30100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

26

μ

PD30100

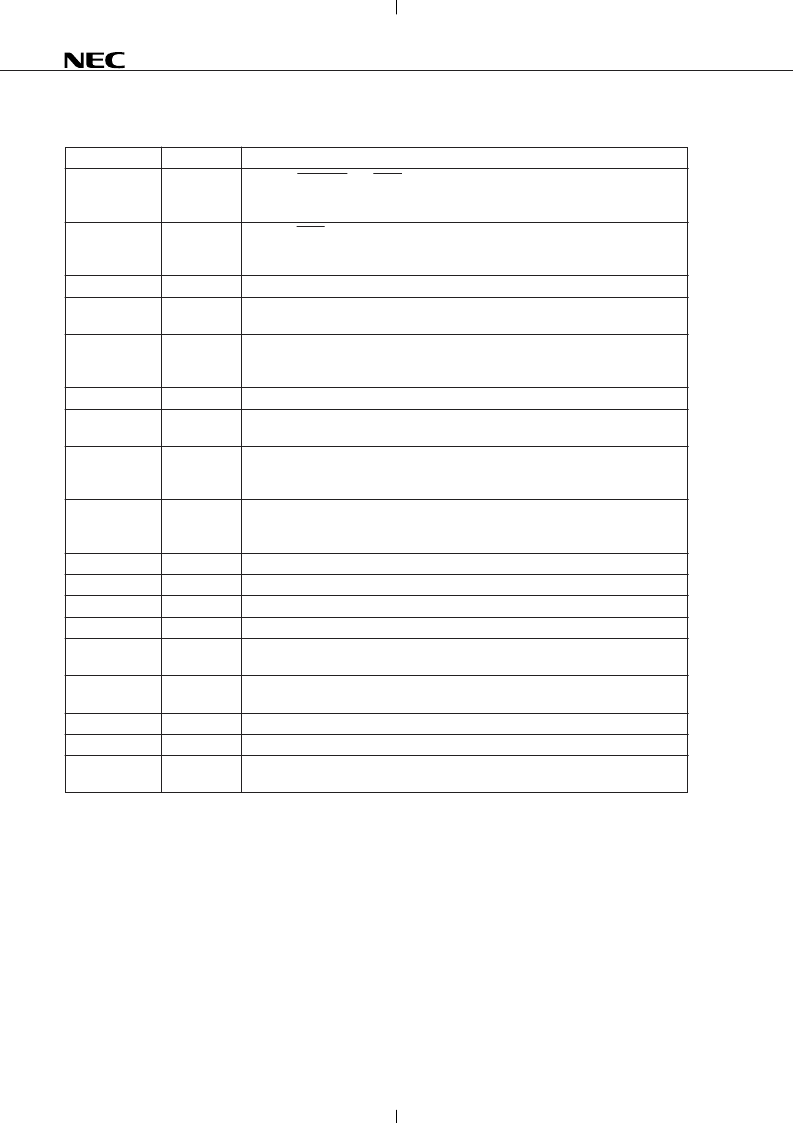

Table 3-4. Types of Exceptions

Exception

Abbreviation

Description

Cold reset

–

Occurs if ColdReset and Reset signals are simultaneously asserted active.

Aborts instruction execution and executes a handler on the reset vector.

The internal status is undefined, except some bits of the status register.

Soft reset

–

Occurs if Reset signal is asserted active.

Aborts instruction execution and executes a handler on the reset vector. The

internal status before soft reset is retained.

NMI

–

Non-maskable interrupt request by the external agent.

TLB unmatch

TLBL/TLBS

Occurs if the operating mode is the 32-bit mode and the number of TLB entries

matching the referenced address runs short.

Expansion

addressing

TLB unmatch

TLBL/TLBS

Occurs if the operating mode is 64-bit mode and the number of TLB entries

matching the referenced address runs short.

TLB invalid

TLBL/TLBS

Occurs if the TLB entry matching the referenced virtual address is invalid. (V bit = 0)

TLB change

Mod

Occurs if a TLB entry that coincides with virtual address to be accessed is valid but

write is disabled (D bit = 0) when the store instruction is executed

Bus error

IBE/DBE

Occurs if an external agent indicates a data error on the SysCmd bus by an external

interrupt to the bus interface (bus timeout, bus parity error, or invalid physical memory

address or access type)

Address error

AdEL/AdES

Occurs if an attempt is made to execute the LH, SH/LW/SW, LD, or SD instruction

to the half word/word/double word not at the half word/word/double word

boundary, or to reference a virtual address that cannot be accessed.

Integer overflow

Ov

Occurs if 2’s complement overflow occurs as a result of addition or subtraction.

Trap

Tr

Occurs if the condition is true at trap instruction execution.

System call

Sys

Occurs when the SYSCALL instruction is executed.

Breakpoint

Bp

Occurs when the BREAK instruction is executed.

Reserved

instruction

RI

Occurs when an instruction whose op code (bits 31-26) is undefined, or the

SPECIAL instruction whose op code (bits 5-0) is undefined is executed.

Coprocessor

unusable

CpU

Occurs if the coprocessor instruction is executed when the corresponding

coprocessor use enable bit is not set.

Interrupt

Int

Occurs when one of the eight interrupt sources becomes active.

Cache error

–

Occurs when a parity error is detected on the internal cache or system interface.

Watch

WATCH

Occurs when an attempt is made to reference the physical address in the watch

Lo/Hi register with the load/store instruction.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD30101 | 64-Bit Microprocessor(64位微處理器) |

| μPD30102 | 64-/32-BIT Microprocessor(64/32位微處理器) |

| μPD30121 | 64-Bit MIPS RISC Microprocessor(64 位RISC 微處理器) |

| μPD30122 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

| μPD30181 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD301-024-03-PC | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Analog IC |

| PD301-024-03-P-C-200 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-P-C-250 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-P-C-300 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-PI | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Analog IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。