- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9687 > XRT91L80IB (Exar Corporation)IC TXRX SONET/SDH 4BIT 196STBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XRT91L80IB |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 29/46頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC TXRX SONET/SDH 4BIT 196STBGA |

| 產(chǎn)品變化通告: | XRT91L80IB Obsolescence 6/Sept/2010 |

| 標(biāo)準(zhǔn)包裝: | 126 |

| 類型: | 收發(fā)器 |

| 規(guī)程: | SONET/SDH |

| 電源電壓: | 3.3V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 196-LFBGA |

| 供應(yīng)商設(shè)備封裝: | 196-STBGA(12x12) |

| 包裝: | 托盤 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

XRT91L80

xr

2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER

REV. 1.0.0

32

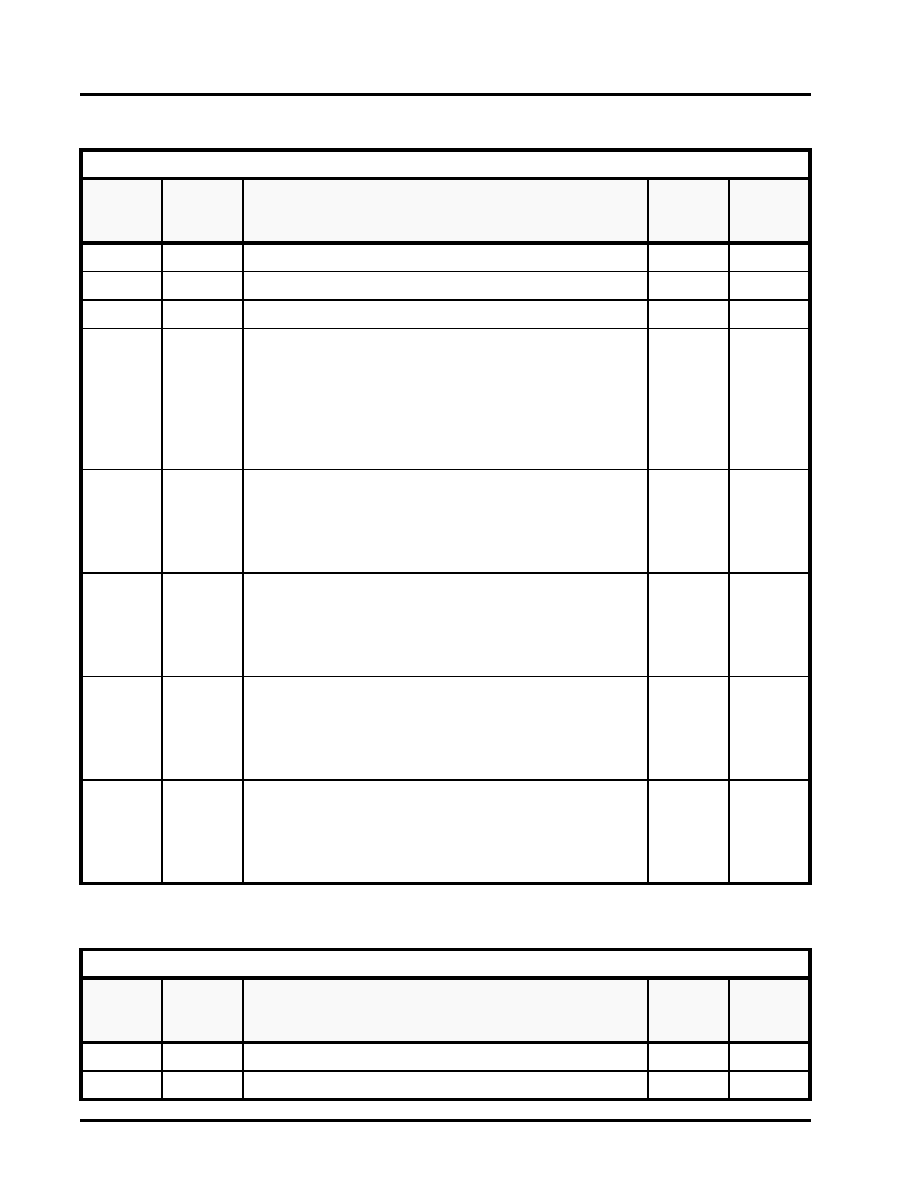

TABLE 13: MICROPROCESSOR REGISTER 0X02H BIT DESCRIPTION

TABLE 12: MICROPROCESSOR REGISTER 0X01H BIT DESCRIPTION

INTERRUPT STATUS CONTROL REGISTER (0X01H)

BIT

NAME

FUNCTION

Register

Type

Default

Value

(HW reset)

D7

Reserved

This Register Bit is Not Used

X

D6

Reserved

This Register Bit is Not Used

X

D5

Reserved

This Register Bit is Not Used

X

D4

VCXOIS

Voltage Controlled External Oscillator Lock Interrupt Status

An external interrupt will not occur unless the VCXOIE is set to "1"

in the channel register 0x00h.

"0" = No Change

"1" = Change in VCXO Lock Status Occurred

NOTE: VCXOLKEN must be enabled for this bit to have functional

meaning.

RUR

0

D3

LOSIS

Loss of Signal Interrupt Status

An external interrupt will not occur unless the RLOSIE is set to "1"

in the channel register 0x00h.

"0" = No Change

"1" = Change in LOS Status Occurred

RUR

0

D2

CDRIS

Clock and Data Recovery Lock Interrupt Status

An external interrupt will not occur unless the CDRIE is set to "1" in

the channel register 0x00h.

"0" = No Change

"1" = Change in CDR Lock Status Occurred

RUR

0

D1

CMUIS

Clock Multiplier Unit Lock Interrupt Status

An external interrupt will not occur unless the CMUIE is set to "1" in

the channel register 0x00h.

"0" = No Change

"1" = Change in CMU Lock Status Occurred

RUR

0

D0

FIFOIS

FIFO Overflow Interrupt Status

An external interrupt will not occur unless the FIFOIE is set to "1" in

the channel register 0x00h.

"0" = No Change

"1" = Change in FIFO Overflow Status Occurred

RUR

0

STATUS CONTROL REGISTER (0X02H)

BIT

NAME

FUNCTION

Register

Type

Default

Value

(HW reset)

D7

Reserved

This Register Bit is Not Used

X

D6

Reserved

This Register Bit is Not Used

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V24B48M150BG2 | CONVERTER MOD DC/DC 48V 150W |

| VI-J52-MX-F1 | CONVERTER MOD DC/DC 15V 75W |

| V24B48M150BF2 | CONVERTER MOD DC/DC 48V 150W |

| VI-J51-MX-F4 | CONVERTER MOD DC/DC 12V 75W |

| V24B36M150BL | CONVERTER MOD DC/DC 36V 150W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L80IB-F | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L81 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L81IB | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82ES | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。