- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9687 > XRT91L80IB (Exar Corporation)IC TXRX SONET/SDH 4BIT 196STBGA PDF資料下載

參數(shù)資料

| 型號: | XRT91L80IB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 21/46頁 |

| 文件大小: | 0K |

| 描述: | IC TXRX SONET/SDH 4BIT 196STBGA |

| 產(chǎn)品變化通告: | XRT91L80IB Obsolescence 6/Sept/2010 |

| 標準包裝: | 126 |

| 類型: | 收發(fā)器 |

| 規(guī)程: | SONET/SDH |

| 電源電壓: | 3.3V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 196-LFBGA |

| 供應商設備封裝: | 196-STBGA(12x12) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

XRT91L80

xr

2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER

REV. 1.0.0

20

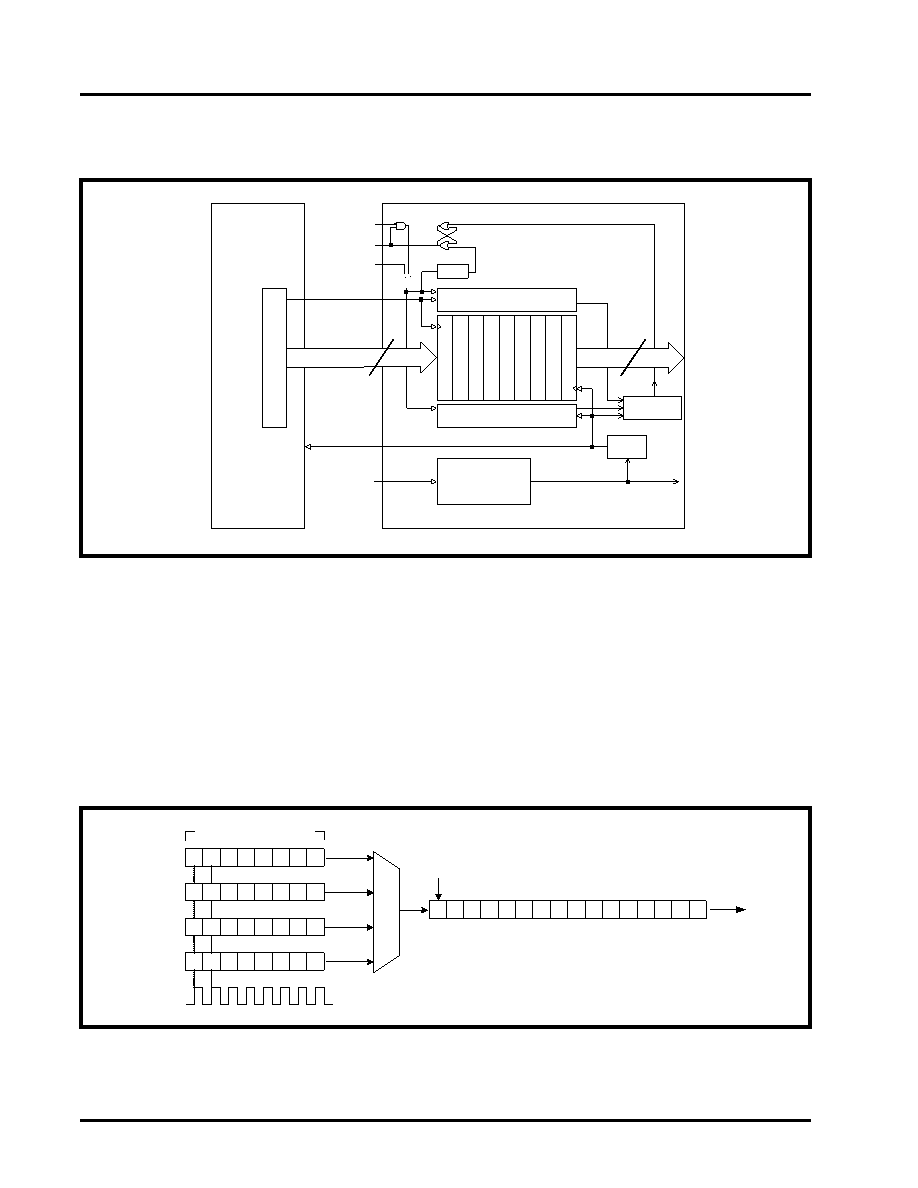

device will set the OVERFLOW pin to a "High" level and will automatically reset and center the FIFO. Figure 11

provides a detailed overview of the transmit FIFO in a system interface.

FIGURE 11. TRANSMIT FIFO AND SYSTEM INTERFACE

3.4

FIFO Calibration Upon Power Up

It is required that the FIFO_RST pin be pulled "High" for 2 TXPCLKOP/N cycles to flush out the FIFO after the

device is powered on. If the FIFO experiences an Overflow condition, FIFO_RST can be used to manually

reset the FIFO. However, the STS-48/STM-16 transceiver has an automatic reset pin that will allow the FIFO to

automatically reset upon an Overflow condition. FIFO_AUTORST should be pulled "High" to enable the

automatic FIFO reset function.

3.5

Transmit Parallel Input to Serial Output (PISO)

The PISO is used to convert 622.08/666.51 MHz parallel data input to 2.488/2.666 Gbps serial data output

which can interface to an optical module. The PISO bit interleaves parallel data input into a serial bit stream

taking the first bit from TXDI3P/N, then the first bit from TXDI2P/N, and so on as shown in Figure 12.

FIGURE 12. SIMPLIFIED BLOCK DIAGRAM OF PISO

Write Pointer

Read Pointer

AUTORST

OVERFLOW

RESET

TXPCLKIP/N

REFCLKP/N

FIFO Control

Div by 4

2.488/2.666 GHz PLL

CMU

delay

Upstream Device

4 x 9 FIFO

XRT91L80

TXPCLKOP/N

4

TXDI[3:0]P/N

4

b00

b01

b02

b03

b04

b05

b06

b07

b10

b11

b12

b13

b14

b15

b16

b17

b20

b21

b22

b23

b24

b25

b26

b27

b30

b31

b32

b33

b34

b35

b36

b37

4-bit Parallel LVDS Data Input

TXDI0P/N

TXDI3P/N

TXDI2P/N

TXDI1P/N

TXOP/N

TXPCLKIP/N

622.08/666.51 MHz

2.488/2.666 Gbps

b00

b10

b20

b30

b01

b11

b21

b31

b02

b12

b22

b32

b03

b13

b23

b33

P

IS

O

time (0)

相關PDF資料 |

PDF描述 |

|---|---|

| V24B48M150BG2 | CONVERTER MOD DC/DC 48V 150W |

| VI-J52-MX-F1 | CONVERTER MOD DC/DC 15V 75W |

| V24B48M150BF2 | CONVERTER MOD DC/DC 48V 150W |

| VI-J51-MX-F4 | CONVERTER MOD DC/DC 12V 75W |

| V24B36M150BL | CONVERTER MOD DC/DC 36V 150W |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L80IB-F | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L81 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L81IB | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82ES | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。