- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4265 > XC3S1400AN-4FGG484I (Xilinx Inc)IC FPGA SPARTAN-3AN 484FPGA PDF資料下載

參數(shù)資料

| 型號: | XC3S1400AN-4FGG484I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 93/123頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3AN 484FPGA |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-3AN |

| LAB/CLB數(shù): | 2816 |

| 邏輯元件/單元數(shù): | 25344 |

| RAM 位總計(jì): | 589824 |

| 輸入/輸出數(shù): | 372 |

| 門數(shù): | 1400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 484-BBGA |

| 供應(yīng)商設(shè)備封裝: | 484-FBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當(dāng)前第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁

DS557 (v4.1) April 1, 2011

Product Specification

71

Copyright 2007–2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and

other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

Introduction

This section describes how the various pins on a Spartan-3AN FPGA connect within the supported component packages,

and provides device-specific thermal characteristics. For general information on the pin functions and the package

characteristics, see the Packaging section of UG331:

UG331: Spartan-3 Generation FPGA User Guide

Spartan-3AN FPGAs are available in Pb-free, RoHS packages, indicated by a “G” in the middle of the package code. Leaded

(Pb) packages are available for selected devices, with the same pinout and without the “G” in the ordering code (see Table 5,

page 7). The Pb-free package code can be selected in the software for the Pb packages since the pinouts are identical.

References to the Pb-free package code in this document apply also to the Pb package.

Pin Types

Most pins on a Spartan-3AN FPGA are general-purpose, user-defined I/O pins. There are, however, up to 12 different

functional types of pins on Spartan-3AN FPGA packages, as outlined in Table 62. In the package footprint drawings that

follow, the individual pins are color-coded according to pin type as in the table.

123

Spartan-3AN FPGA Family:

Pinout Descriptions

DS557 (v4.1) April 1, 2011

Product Specification

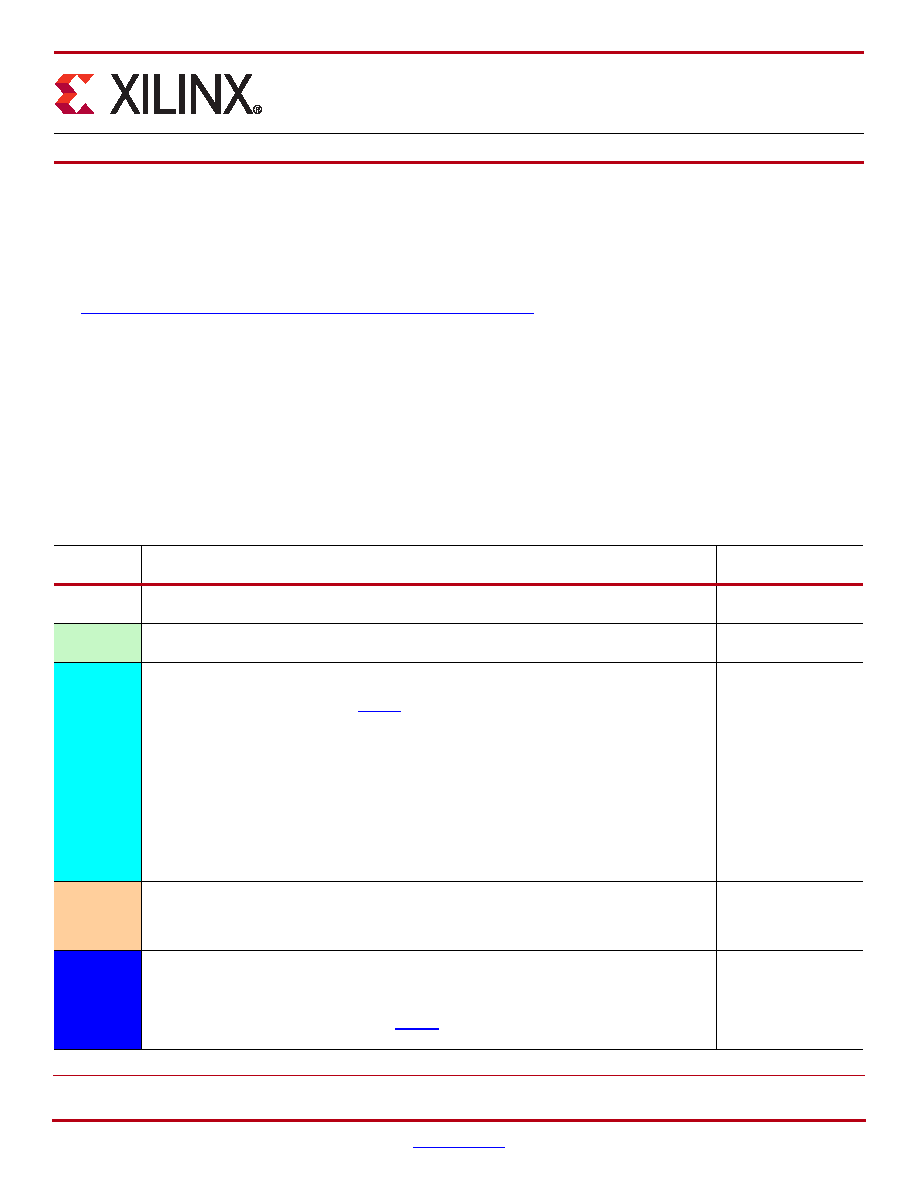

Table 62: Types of Pins on Spartan-3AN FPGAs

Type with

Color Code

Description

Pin Name(s) in

Type(1)

I/O

Unrestricted, general-purpose user-I/O pin. Most pins can be paired together to form differential

I/Os.

IO_#

IO_Lxxy_#

INPUT

Unrestricted, general-purpose input-only pin. This pin does not have an output structure,

differential termination resistor, or PCI clamp diode.

IP_#

IP_Lxxy_#

DUAL

Dual-purpose pin used in some configuration modes during the configuration process and then

usually available as a user I/O after configuration. If the pin is not used during configuration, this

pin behaves as an I/O-type pin. See UG332: Spartan-3 Generation Configuration User Guide for

additional information on these signals.

M[2:0]

PUDC_B

CCLK

MOSI/CSI_B

D[7:1]

D0/DIN

DOUT

CSO_B

RDWR_B

INIT_B

A[25:0]

VS[2:0]

LDC[2:0]

HDC

VREF

Dual-purpose pin that is either a user-I/O pin or Input-only pin, or, along with all other VREF pins

in the same bank, provides a reference voltage input for certain I/O standards. If used for a

reference voltage within a bank, all VREF pins within the bank must be connected.

IP/VREF_#

IP_Lxx_#/VREF_#

IO/VREF_#

IO_Lxx_#/VREF_#

CLK

Either a user-I/O pin or an input to a specific clock buffer driver. Most packages have 16 global

clock inputs that optionally clock the entire device. The exceptions are all devices in the TQG144

package and the XC3S50AN in the FTG256 package. The RHCLK inputs optionally clock the

right half of the device. The LHCLK inputs optionally clock the left half of the device. See the

Using Global Clock Resources chapter in UG331: Spartan-3 Generation FPGA User Guide for

additional information on these signals.

IO_Lxx_#/GCLK[15:0],

IO_Lxx_#/LHCLK[7:0],

IO_Lxx_#/RHCLK[7:0]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7-745129-4 | CONN FERRULE CRIMP DB 3,5 |

| 5748271-1 | CONN SCREW LOCKS FMALE KIT 4-40 |

| 7-745129-9 | CONN FERRULE CRIMP DB9,15,50 |

| 1-750877-9 | CONN TERM COVER 100POS .050 |

| ABB100DHLD | CONN EDGECARD 200PS .050 DIP SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S1400AN-4FGG676C | 功能描述:IC SPARTAN-3AN FPGA 1400K 676FBG RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3AN 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計(jì):221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC3S1400AN-4FGG676CES | 制造商:Xilinx 功能描述: |

| XC3S1400AN-4FGG676I | 功能描述:IC FPGA SPARTAN-AN 1400K 676FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3AN 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S1400AN-5FG484C | 制造商:Xilinx 功能描述:SPARTAN3AN - Trays 制造商:Xilinx 功能描述:IC FPGA 372 I/O 484FBGA |

| XC3S1400AN-5FG676C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3AN FAMILY 1.4M GATES 25344 CELLS 770MHZ 90NM T - Trays 制造商:Xilinx 功能描述:IC FPGA 502 I/O 676FBGA 制造商:Xilinx 功能描述:IC SPARTAN-3AN FPGA 1400K 676BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。