- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384021 > TMS320C6727B_07 (Texas Instruments, Inc.) Floating-Point Digital Signal Processors PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320C6727B_07 |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | Floating-Point Digital Signal Processors |

| 中文描述: | 浮點(diǎn)數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 104/116頁(yè) |

| 文件大小: | 999K |

| 代理商: | TMS320C6727B_07 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)當(dāng)前第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)

www.ti.com

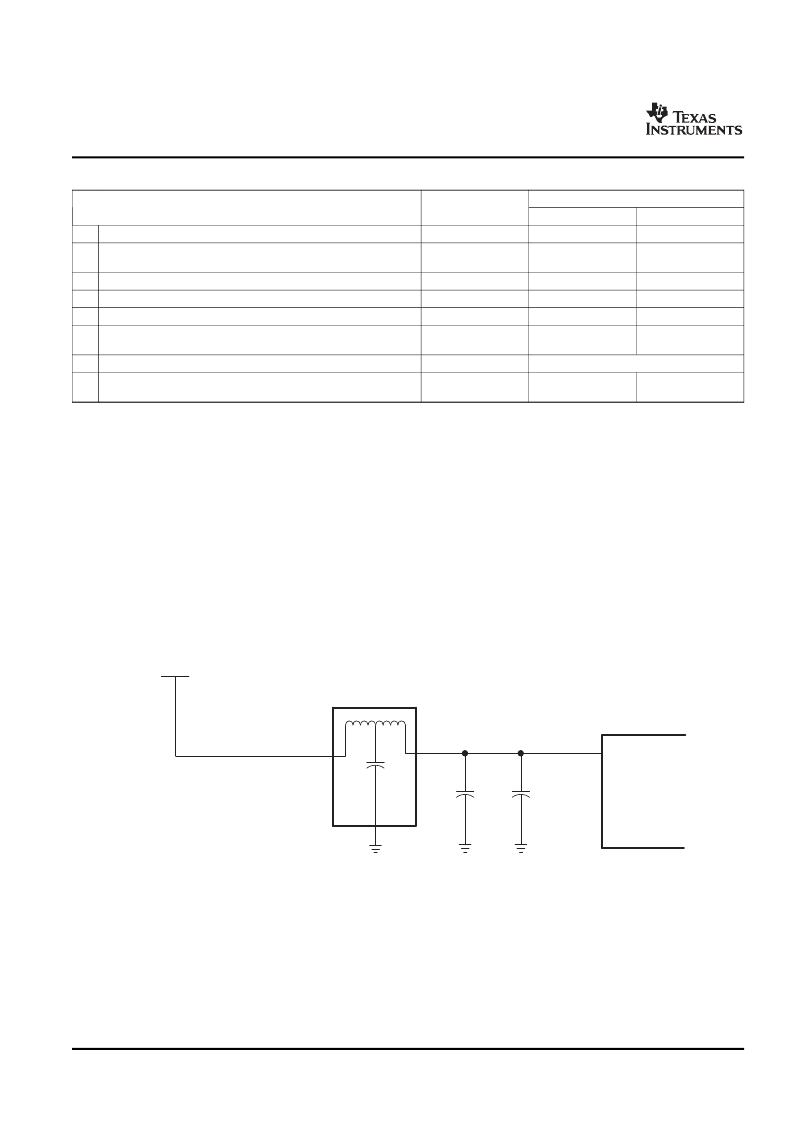

BOARD

DV

DD

(3.3 V)

EMI

Filter

10 F

0.1 F

PLLHV

Place Filter and Capacitors as Close

to DSP as Possible

EMI Filter: TDK ACF451832333, 223, 153, or 103,

Panasonic EXCCET103U, or Equivalent

+

TMS320C6727B, TMS320C6726B, TMS320C6722B, TMS320C6720

Floating-Point Digital Signal Processors

SPRS370C–SEPTEMBER 2006–REVISED OCTOBER 2007

Table 4-42. Allowed PLL Operating Conditions

ALLOWED SETTING OR RANGE

MIN

125 ns

187.5 μs

PARAMETER

DEFAULT VALUE

MAX

1

2

PLLRST = 1 assertion time during initialization

Lock time before setting PLLEN = 1. After changing D0, PLLM, or

input clock.

PLL input frequency (PLLREF after D0

(1)

)

PLL multiplier values (PLLM)

PLL output frequency (PLLOUT before dividers D1, D2, D3)

(2)

SYSCLK1 frequency (set by PLLM and dividers D0, D1)

N/A

N/A

3

4

5

6

12 MHz

x4

140 MHz

50 MHz

x25

600 MHz

x13

N/A

PLLOUT/1

Device Frequency

Specification

7

8

SYSCLK2 frequency (set by PLLM and dividers D0, D2)

SYSCLK3 frequency (set by PLLM and dividers D0, D3)

PLLOUT/2

PLLOUT/3

/2, /3, or /4 of SYSCLK1

EMIF Frequency

Specification

(1)

(2)

Some values for the D0 divider produce results outside of this range and should not be selected.

In general, selecting the PLL output clock rate closest to the maximum frequency will decrease clock jitter.

CAUTION

SYSCLK1, SYSCLK2, SYSCLK3 must be configured as aligned by setting ALNCTL[2:0]

to '1'; and the PLLCMD.GOSET bit must be written every time the dividers D1, D2, and

D3 are changed in order to make sure the change takes effect and preserves

alignment.

CAUTION

When changing the PLL parameters which affect the SYSCLK1, SYSCLK2, SYSCLK3

dividers, the bridge BR2 in

Figure 2-4

must be reset by the CFGBRIDGE register. See

Table 2-7

.

The PLL is an analog circuit and is sensitive to power supply noise. Therefore it has a dedicated 3.3-V

power pin (PLLHV) that should be connected to DV

DD

at the board level through an external filter, as

illustrated in

Figure 4-44

.

Figure 4-44. PLL Power Supply Filter

104

Peripheral and Electrical Specifications

Submit Documentation Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320DM355_07 | Digital Media System-on-Chip (DMSoC) |

| TMS320DM6446_07 | Digital Media System-on-Chip |

| TMS320F2801X | Digital Signal Processors |

| TMS320F2809_07 | Digital Signal Processors |

| TMS320F28335_1 | Variable Capacitance Diode for TV Tuner VHF Tuning; Ratings VR (V): 32; Characteristics n: 12.0 min; Characteristics rs (ohm) max: 0.85; Characteristics C (pF) max: C2 = 32.2 to 37.5 C25 = 2.57 to 3.0; Characteristics CVR/CVR: 2/25; Cl: 2.777; Package: UFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320C6727BGDH275 | 制造商:Texas Instruments 功能描述:DSP FLOATING PT 32BIT/64BIT 275MHZ 2200MIPS 256BGA - Trays |

| TMS320C6727BGDH300 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Floating-Point DSP RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320C6727BGDH350 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Floating-Point DSP RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320C6727BZDH250 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Floating-Pt Dig RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320C6727BZDH275 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Floating-Point DSP RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。