- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98071 > S5933QE (APPLIEDMICRO INC) PCI BUS CONTROLLER, PQFP160 PDF資料下載

參數(shù)資料

| 型號: | S5933QE |

| 廠商: | APPLIEDMICRO INC |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PQFP160 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁數(shù): | 165/176頁 |

| 文件大小: | 823K |

| 代理商: | S5933QE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁當(dāng)前第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁

3-101

PCI BUS INTERFACE

S5933

PCI BUS MASTERSHIP

When the S5933 requires PCI bus mastership, it pre-

sents a request via the REQ# signal. This signal is

connected to the system’s PCI bus arbiter.

Only one initiator (bus master) may control the PCI

bus at a given time. The bus arbiter determines

which initiator is given control of the bus. Control is

granted to a requesting device by the arbiter assert-

ing that device’s grant signal (GNT#). Each REQ#/

GNT# signal pair is unique to a given PCI agent.

After asserting REQ#, the S5933 assumes bus own-

ership on the first PCI clock edge where its GNT#

input is asserted along with FRAME# and IRDY#

deasserted (indicating no other device is generating

PCI bus cycles). Once ownership is established by

the S5933, it maintains ownership as long as the

arbiter keeps its GNT# asserted. If GNT# is

deasserted, the S5933 completes the current trans-

action. The S5933 does this by deasserting FRAME#

and then deasserting IRDY# upon data transfer. Fig-

ure 13 shows a sequence where the S5933 is

granted ownership of the bus and then is preempted

by another master before the S5933 can finish its

current transaction.

Bus Mastership Latency Components

It is often necessary for system designers to predict

and guarantee that a minimum data transfer rate is

sustainable to support a particular application. In the

design of a bus mastering application, knowledge of

the maximum delay a device might encounter from

the time it requests the PCI bus to the time in which it

is actually granted the bus is desirable. This allows

the design to provide adequate data buffering. The

PCI specification refers to this bus request to grant

delay as “arbitration latency.”

Once a PCI initiator has been granted the bus, the

PCI specification defines the delay from the grant to

the new initiator’s assertion of FRAME# as the “bus

acquisition latency.” Afterwards, the delay from

FRAME# asserted to target ready (TRDY#) asserted

is defined as “target latency.” Figure 14 shows a

time-line depicting the components of PCI bus ac-

cess latency.

There are numerous configuration variations possible

with the PCI specification. A system designer can

determine whether a bus master can support a criti-

cal, timely transfer by establishing a specific configu-

ration and by defining these latency values. The

S5933, as an initiator, produces the fastest response

allowable for its bus acquisition latency (GNT# to

FRAME# asserted). The S5933 also implements the

PCI Master Latency Timer. Once granted the bus,

the S5933 is guaranteed ownership for a minimum

amount of time defined by the Master Latency Timer.

The S5933, as an initiator, cannot control the respon-

siveness of a particular target nor the bus arbitration

delay.

The PCI specification provides two mechanisms to

control the amount of time a master may own the

bus. One mechanism is through the master (master-

initiated termination). The other is by the target and is

achieved through a target-initiated disconnect.

Bus Arbitration

Although the PCI specification defines the condition

that constitutes bus ownership, it does not provide

rules to be used by the system’s PCI bus arbiter in

deciding which master is to be granted the PCI bus

next. The arbitration priority scheme implemented by

a system may be fixed, rotational, or custom. The

arbitration latency is a function of the system, not the

S5933.

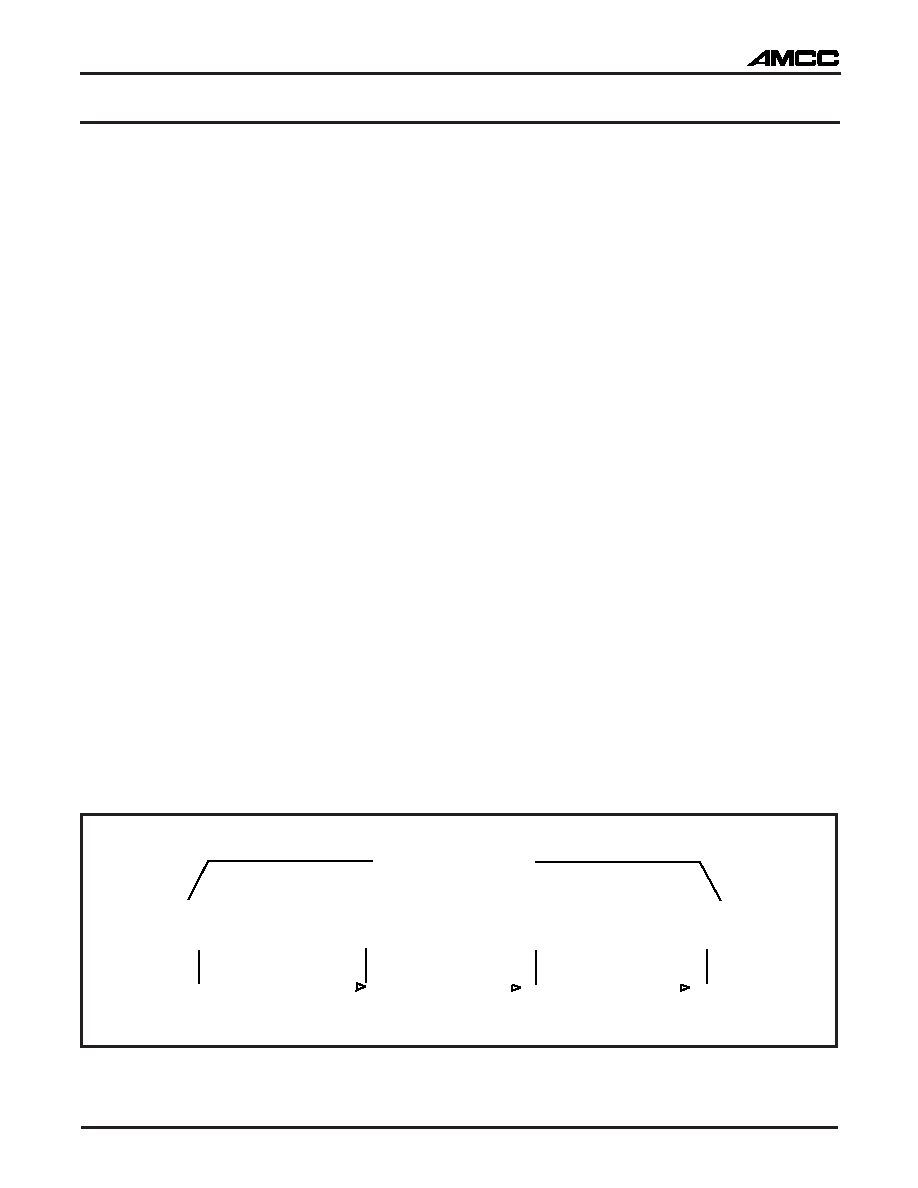

Figure 14. PCI Bus Access Latency Components

Bus Access Latency

REQ#

Asserted

GNT#

Asserted

FRAME#

Asserted

TRDY#

Asserted

--Arbitration Latency--

--Bus Acquisition--

Latency

--Target Latency--

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S6A0032 | 16 X 80 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC138 |

| S6A0069 | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC80 |

| S6A0078 | 34 X 120 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC183 |

| S80296SA40 | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| S80486-DX4-75-S-V-8-B | 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S5935 | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PCI Product |

| S5935_07 | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PCI Product |

| S59355QRC | 制造商:AppliedMicro 功能描述: |

| S5935QF | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PCI Product |

| S5935QRC | 制造商:AppliedMicro 功能描述:PCI Master Device 160-Pin PQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。