- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382380 > PCD5003A (NXP Semiconductors N.V.) Enhanced Pager Decoder for POCSAG PDF資料下載

參數(shù)資料

| 型號(hào): | PCD5003A |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Enhanced Pager Decoder for POCSAG |

| 中文描述: | 增強(qiáng)傳呼機(jī)POCSAG碼解碼器 |

| 文件頁(yè)數(shù): | 18/44頁(yè) |

| 文件大小: | 233K |

| 代理商: | PCD5003A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

1999 Jan 08

18

Philips Semiconductors

Product specification

Enhanced Pager Decoder for POCSAG

PCD5003A

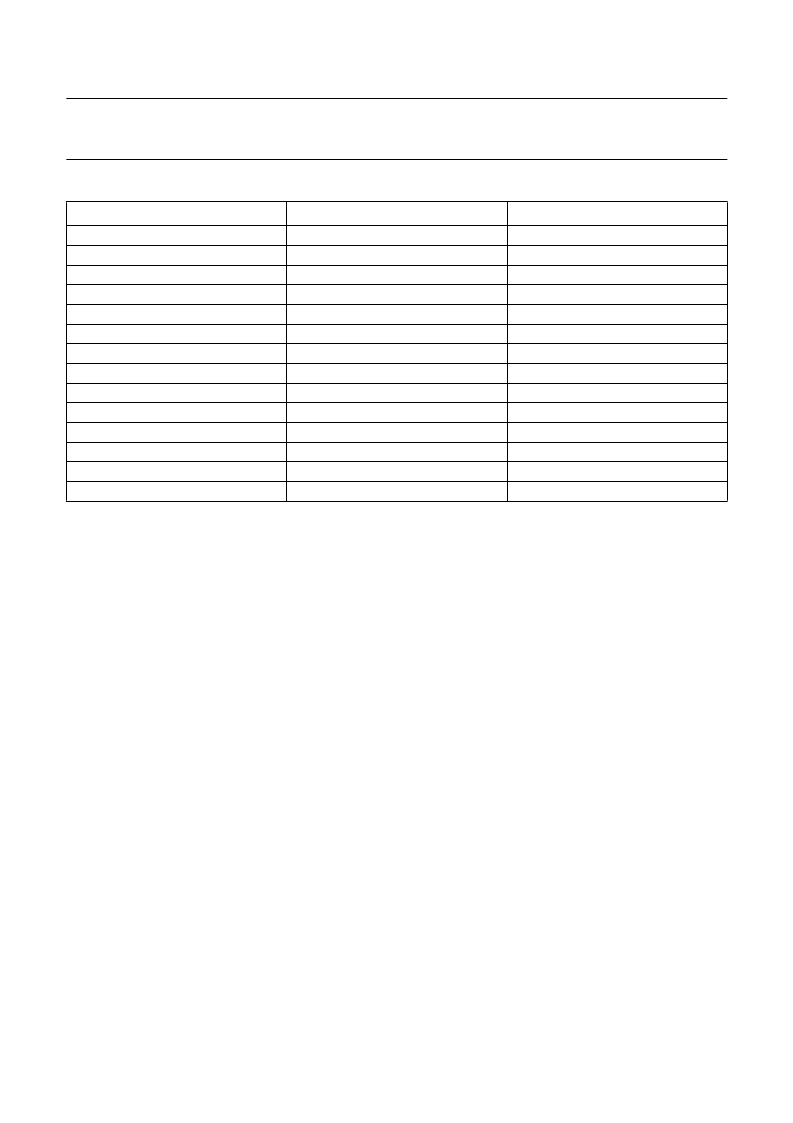

Table 13

Index register

Notes

1.

2.

The index register only uses the least significant nibble, the upper 4 bits are ignored.

Writing to registers 0B to 0F has no effect, reading produces meaningless data.

ADDRESS

(1)

REGISTER FUNCTION

ACCESS

00H

00H

01H

02H

03H

04H

05H

05H

06H

07H

08H

09H

0AH

status

control

R

W

real-time clock: seconds

real-time clock:

1

100

second

alert cadence

alert set-up

periodic interrupt modulus

periodic interrupt counter

RAM write address pointer

EEPROM address pointer

RAM read address pointer

RAM data output

EEPROM data input/output

unused

R/W

R/W

W

W

W

R

R

R/W

R/W

R

R/W

note 2

0BH to 0FH

7.26

External interrupt

The PCD5003A can signal events to an external controller

via an interrupt signal on output INT. The interrupt polarity

is programmable via SPF programming. The interrupt

source is shown in the status register.

Interrupts are generated by the following events (more

than one event possible):

Call data available for output (bit D2)

SRAM pointers becoming equal (bit D3)

Expiry of periodic time-out (bit D7)

Expiry of alert time-out (bit D4)

Change of state in out-of-range indicator (bit D5)

Change of state in battery-low indicator or in receiver

control output RXE (bit D6).

Immediate interrupts are generated by status bits D3,

D4, D6 (RXE monitoring) and D7. Bits D2, D5 and D6

(BAT monitoring) generate interrupts as soon as the

receiver is disabled (RXE = 0).

When call data is available (D2 = 1) but the receiver

remains switched on, an interrupt is generated at the next

sync word position, if data fail mode (short fade recovery

mode in APOC1) is not active.

The interrupt output INT is reset after completion of a

status read operation.

7.27

Interrupt Masking

In the PCD5003A certain interrupts can be suppressed by

masking via the control register. This feature prevents

unnecessary wake-up actions of the microcontroller

causing battery life reduction.

The following interrupts can be masked:

Out-of-Range (status bit D5)

: change of state

interrupt, masked by setting control register bit D5

BAT/RXE monitoring (status bit D6)

: change of state

interrupt (source selected by control register bit D2),

masked by setting control register bit D6

Periodic Timer (status bit D7)

: timer overflow interrupt,

masked by setting control register bit D7.

Although no interrupts are generated by these conditions

when masked via the control register, the corresponding

status bits are normally updated and available via the

status register. At reset the control register is cleared,

causing all interrupts to be enabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD5003AH | Enhanced Pager Decoder for POCSAG |

| PCD5003 | Advanced POCSAG Paging Decoder |

| PCD5003H | Advanced POCSAG Paging Decoder |

| PCD5008 | FLEX Pager Decoder |

| PCD5008H | FLEX Pager Decoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD5003AH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced Pager Decoder for POCSAG |

| PCD5003H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

| PCD5003HB-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication Decoder |

| PCD5003U/10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

| PCD5008 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:FLEX Pager Decoder |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。